FPGA/CPLD状态机的稳定性设计

随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA技术的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无处不在.在FPGA/CPLD设计中,状态机是最典型、应用最广泛的时序电路模块,如何设计一个稳定可靠的状态机是我们必须面对的问题.

1、状态机的特点和常见问题

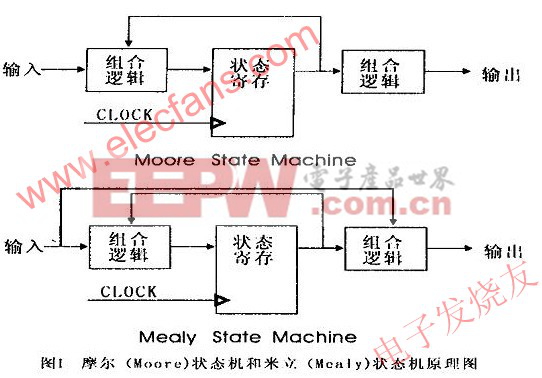

标准状态机分为摩尔(Moore)状态机和米立(Mealy)状态机两类.Moore状态机的输出仅与当前状态值有关,且只在时钟边沿到来时才会有状态变化.Mealy状态机的输出不仅与当前状态值有关,而且与当前输入值有关,这一特点使其控制和输出更加灵活,但同时也增加了设计复杂程度.其原理如图1所示.

根据图1所示,很容易理解状态机的结构.但是为什么要使用状态机而不使用一般时序电路呢?这是因为它具有一些一般时序电路无法比拟的优点.

用VHDL描述的状态机结构分明,易读,易懂,易排错;

相对其它时序电路而言,状态机更加稳定,运行模式类似于CPU,易于实现顺序控制等.

用VHDL语言描述状态机属于一种高层次建模,结果经常出现一些出乎设计者意外的情况:

在两个状态转换时,出现过渡状态.

在运行过程中,进入非法状态.

在一种器件上综合出理想结果,移植到另一器件上时,不能得到与之相符的结果.

状态机能够稳定工作,但占用逻辑资源过多.

在针对FPGA器件综合时,这种情况出现的可能性更大.我们必须慎重设计状态机,分析状态机内在结构,在Moore状态机中输出信号是当前状态值的译码,当状态寄存器的状态值稳定时,输出也随之稳定了.经综合器综合后一般生成以触发器为核心的状态寄存电路,其稳定性由此决定.如果CLOCK信号的上升沿到达各触发器的时间严格一致的话,状态值也会严格按照设计要求在规定的状态值之间转换.然而这只是一种理想情况,实际CPLD/FPGA器件一般无法满足这种苛刻的时序要求,特别是在布线后这些触发器相距较远时,CLOCK到达各触发器的延时往往有一些差异.这种差异将直接导致状态机在状态转换时产生过渡状态,当这种延时进一步加大时,将有可能导致状态机进入非法状态.这就是Moore状态机的失效机理.对于Mealy状态机而言,由于其任何时刻的输出与输入有关,这种情况就更常见了.

2 状态机设计方案比较

2.1 采用枚举数据类型定义状态值

在设计中定义状态机的状态值为枚举数据类型,综合器一般把它表示为二进制数的序列,综合后生成以触发器为核心的状态寄存电路,寄存器用量会减少,其综合效率和电路速度将会在一定程度上得到提高.

例1 定义状态值为枚举类型的状态机VHDL程序.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

end example;

architecture behave of example is

type states is(st0,st1,st2,st3); --定义states为枚举类型

signal current_state,next_state:states;

begin

state_change:process(clk) --状态改变进程

begin

wait until clk'event and clk='1';

current_state=next_state;

end process state_change;

combination:process(current_state,mach_input)

…… --输出状态值译码,给next_state赋新值.省略

end behave;

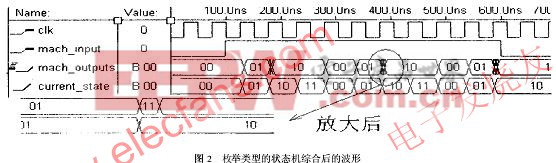

图2 枚举类型的状态机综合后的波形

例1是一个四状态全编码状态机,综合后的仿真波形如图2所示.从放大后的局部可以看出输出状态值从“01”到“10”转换过程中出现了过渡状态“11”.从微观上分析中间信号“Current_state”状态转换过程,状态寄存器的高位翻转和低位翻转时间是不一致的,当高位翻转速度快时,会产生过渡状态“11”,当低位翻转速度快时会产生过渡状态“00”.若状态机的状态值更多的话,则产生过渡状态的概率更大.如果在非全编码状态机中,由于这种过渡状态的反馈作用,将直接导致电路进入非法状态,若此时电路不具备自启动功能,那么电路将无法返回正常工作状态.

因为状态机的输出信号常用作重要的控制,如:三态使能,寄存器清零等.所以这种结果是不允许的,如何消除此类过渡状态呢?方法之一是采用格雷码表示状态值.

2.2 用格雷码表示状态值

格雷码的特点是任意相邻两个数据之间只有一位不同,这一特点使得采用格雷码表示状态值的状态机,可以在很大程度上消除由延时引起的过渡状态.将例1改进之后的程序如例2.

例2 采用格雷码表示状态值的状态机.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)