FPGA/EPLD的自上而下设计方法

FPGA/EPLD的自上而下(Top-Down)设计方法:

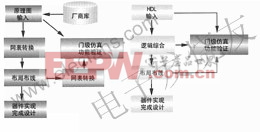

传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特定FPGA/EPLD厂商布局布线器所需网表,通过布局布线,完成设计。原理图绘制完成后可采用门级仿真器进行功能验证。

图1:传统的设计手段与Top-Down设计工具的比较

然而,工程师的最初设计思想不是一开始就考虑采用某一FPGA/EPLD厂商的某一特定型号器件,而是从功能描述开始的。设计工程师首先要考虑规划出能完成某一具体功能、满足自己产品系统设计要求的某一功能模块,利用某种方式(如HDL硬件描述语言)把功能描述出来,通过功能仿真(HDL仿真器)以验证设计思路的正确性。当所设计功能满足需要时,再考虑以何种方式(即逻辑综合过程)完成所需要的设计,并能直接使用功能定义的描述。实际上这就是自顶而下设计方法。

与传统电原理图输入设计方法相比,Top-Down设计方法具体有以下优点:

1、完全符合设计人员的设计思路,从功能描述开始,到物理实现的完成。

2、功能设计可完全独立于物理实现

在采用传统的电原理输入方法时,FPGA/EPLD器件的采用受到器件库的制约。由于不同厂商FPGA/EPLD的结构完全不同,甚至同一厂商不同系列的产品也存在结构上的差别,因此,在设计一开始,工程师的设计思路就受到最终所采用器件的约束,大大限制了设计师的思路和器件选择的灵活性。而采用Top-Down设计方法,功能输入采用国际标准的HDL输入方法,HDL可不含有任何器件的物理信息,因此工程师可以有更多的空间去集中精力进行功能描述,设计师可以在设计过程的最后阶段任意选择或更改物理器件。

3、设计可再利用

设计结果完全可以以一种知识产权(IP-Intellectual Property)的方式作为设计师或设计单位的设计成果,应用于不同的产品设计中,做到成果的再利用。

4、易于设计的更改

设计工程师可在极短的时间内修改设计,对各种FPGA/EPLD结构进行设计结果规模(门消耗)和速度(时序)的比较,选择最优方案。

5、设计、处理大规模、复杂电路

目前的FPGA/EPLD器件正向高集成度、深亚微米工艺发展。为设计系统的小型化,低功耗、高可靠性等提供了集成的手段。设计低于一万门左右的电路,Top-Down设计方法具有很大的帮助,而设计更大规模的电路,Top-Down设计方法则是必不可少的手段。

6、设计周期缩短,生产率大大提高,产品上市时间提前,性能明显提高,产品竞争力加强。据统计,采用Top-Down设计方法的生产率可达到传统设计方法的2到4倍。

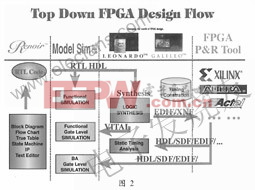

Top-Down设计流程如图2所示,其核心是采用HDL语言进行功能描述,由逻辑综合(Logic Synthesis)把行为(功能)描述转换成某一特定FPGA/EPLD的工艺网表,送到厂商的布局布线器完成物理实现。在设计过程的每一个环节,仿真器的功能验证和门级仿真技术保证设计功能和时序的正确性。

FPGA/EPLD To p-Down 设计工具的黄金组合

Mentor Graphics公司提供一整套基于UNIX平台和Windows 95/NT 平台的FPGA/EPLD Top-Down设计工具:Renoir/ModelSim 和Exemplar,如图2所示。两种平台的工具具有相同的用户界面,并保证数据库的完全统一。目前,在FPGA/EPLD Top-Down设计方法全球市场上,Mentor已拥有42%的市场份额,远远领先于其他任何一个厂家。

采用Top-Down设计方法进行FPGA/EPLD设计,其设计结果的优劣与否取决于三个重要的因素:描述手段(即HDL语言)、设计方法(Style)和设计工具。描述手段是基础,设计方法需要工程经验,而设计工具则是Top-Down设计的关键。一套完整、强大、性能卓越的设计工具,可帮助设计工工程师最大限度的发挥其设计能力。

1. 图形化输入工具-Renoir

----设计工程师采用Top-Down方法进行FPGA/EPLD设计所面临到的第一个问题就是HDL语言的学习。语言的学习过程和应用能力直接影响设计产品的完成及其性能。但是设计师进行产品设计的最初并不是考虑如何去写语言,而是习惯于画出设计的框图,并采用图形化方法(流程图、状态图、真值表等)把它描述出来。Renoir这一图形化输入工具,不仅可以帮助设计师完成产品的功能描述,更可以自动生成HDL语言,为逻辑综合提供必要的输入数据。

---- 采用图形化输入方法主要优点体现在:

提供框图、流程图、状态图、真值表等图形输入方法,使设计工程师从纯文本的设计方法理解脱出来,设计手段更贴近于设计师的思维过程:

便于工程师之间进行设计的相互交流以及对前人/他人设计结果的理解与再利用; 便于初学者学习HDL语言;

便于设计成

- 基于FPGA的DSP设计方法(08-26)

- 专家指导:Linux操作系统密码恢复方法(05-16)

- 基于多核DSP Bootload代码加载方法研究(01-16)

- 基于DSP 的大容量无线传输技术中高性能的启动方法(03-16)

- 多核调试新方法探讨(10-22)

- 有备无患Linux操作系统备份方法介绍(06-06)