适用于嵌入式系统的AES加密IP核设计

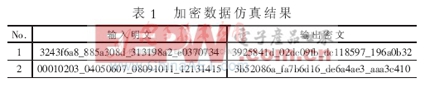

将此综合结果在ModelSim中用133 MHz时钟驱动进行后仿真。 4 数据分析 仿真结果见表1,No.1采用常用测试数据,密钥为:2b7e1516_28aed2a6_abf71588_09cf4f3c,输入明文为3243f6a8_885a308d_313198a2_e0370734时,得到输出密文3925841d_02dc09fb_dc118597_196a0b32,结果正确无误。 该IP核工作在80 MHz时钟频率下时,数据吞吐量为128 bit×80 MHz/40 clk=256 Mb/s。速度/资源比(Mb/s)/Slice=256/(2647/2)=0.193。当并行连接IP核进行位宽扩展时,密钥扩展单元与时序控制单元可共用,进一步提高资源利用率。当扩展为128位数据位宽时,数据吞吐量成倍增加,而速度/资源比也有所提高,几乎能达到 (Mb/s)/Slice=1024/((2647×4-(1388+45)×3)/2)=0.326。 表2中数据显示本设计在32位数据位宽的同类设计中有一定的优势,从适用于嵌入式系统应用的角度考虑,本设计更具优越性。128位数据位宽的设计[6]中原文计算速度/资源比值时未考虑所占用的RAMs资源,而且文中设计为25 MHz时钟频率,进行数据分析时却将工作频率直接换算为54 MHz,而未对其设计是否可正常工作于此频率进行论证。其设计主要考虑建立流水作业以提高性能。参考文献[6]中采用6级流水线技术及复合域方法优化Sbox,达到了较优的设计指标,但其固定的128位数据位宽在嵌入式系统中应用有一定的局限性。 在Synplify9下选定目标器件EP2S15F484C3,优先考虑提高速度,综合结果报告最高时钟频率超过240 MHz,说明本IP核设计合理,较好地利用了目标器件资源。如果将本IP核应用在更高性能目标器件上或是设计为ASIC将会有更大的性能提升。 本文设计的IP核在低端FPGA能以较低的资源消耗提供I/O性能,AES实现达到256 Mb/s,并提供适合应用于嵌入式系统中32位数据界面。在输入、输出端加FIFO数据缓存器可减少主器件被中断数据传输的次数,提供标准通信界面、简化主器件的操作时序。该IP核具有一定的灵活性,可将数据位宽扩展为64位或128位等,满足多种数据位宽应用的要求,是一种低成本高性能的AES加密实现方法。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 嵌入式系统中文输入法的设计(03-02)

- 基于MPC755的嵌入式计算机系统设计(05-10)

- WinCE下光电编码器的驱动程序设计(04-12)

- 为什么嵌入式开发人员要使用FPGA(05-13)

- VxWorks几种常用的延时方法介绍(05-16)