适用于嵌入式系统的AES加密IP核设计

Rijndael加密算法于2000年被确定为美国高级加密标准AES(Advanced Encryption Standard),现在己是工业界数据加密的通用标准之一。Rijndael算法无论从理论分析,还是在实践应用都表现出很好的抵抗各种攻击的性能,其安全性是不容置疑的。

随着计算机技术、微电子技术的不断融合,嵌入式系统应用得到了迅猛发展。近年来嵌入式技术广泛用于解决保密信息的传输、存储和管理方面的问题。而这些都需要嵌入式系统集成有可靠的加密模块。现有一些应用中的加密模块还不尽如人意。本文针对此应用需求设计一种适用于嵌入式系统的加密IP核。

1 AES算法

1.1 AES算法描述

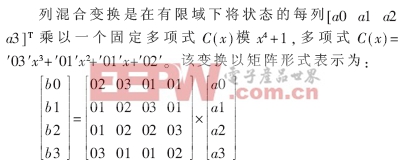

密钥密码体制分为流密码和分组密码两种。分组密码是信息与网络安全中实现数据加密、数字签名、认证及密钥管理的核心体制,具有速度快、易于标准化和便于软硬件实现等特点。AES采用分组密码的加密方式,其分组长度分为128 bit、192 bit、256 bit三种,AES密码在相同的轮函数作用下,迭代运算次数的不同可达到不同级别的安全强度。128 bit分组长度的情况下,循环轮数指定为11次,目前还没有可行的算法可以对该模型进行有效攻击[1]。每一轮处理均为作用在中间结果上的一批运算,该中间结果称为状态,用4×4字节矩阵表示,其中,数据矩阵称为State、密钥矩阵称为Key。AES加密涉及5种运算,分别是字节代换(SubBytes)、行移变换(ShiftRows)、列混合变换(MixColumns)、密钥加法(AddRoundKey)和密钥扩展(ExpandedKey)。

字节代换是对State每个字节进行独立非线性变换,由字节在GF(28)域中求其乘法逆并外加一个仿射变换完成[2]。具体实现中广泛使用查表方式完成该步变换(实现该功能单元被称为Sbox),以避免复杂的乘法运算。

行移变换是对State进行按行移位操作,第0行不移位,第1行循环左移一位,第2行循环左移两位,第3行循环左移三位。

密钥加法是将轮密钥Key和状态State中对应字节按位“异或”。

密钥扩展提供轮变换对应密钥加法用到的各轮密钥。各轮运算中使用到的轮密钥都不相同,密钥扩展运算通过控制迭代运算次数计算出对应轮所需轮密钥[3]。

加密过程由11轮运算组成,其中首轮只进行密钥加法,接着进行9次轮变换,轮变换由字节代换、行移变换、列混合变换及密钥加法4个步骤构成,再进行末轮变换,在末轮中跳过列混合变换。末轮完成后输出密文数据。AES加密过程如图1所示。

1.2 常用AES优化实现

AES算法的轮操作特点看似更适合于在通用CPU平台下编程实现,而实际上,此种实现方式在性能方面存在加密速度慢等先天局限性。AES加密处理单元一般处于数据主干道上,其处理数据能力直接影响整个应用系统的外在性能表现,因此,研究数据处理能力强的硬件加密实现方式具有重要的意义。如何实现高性价比的硬件AES加密一直是加密算法应用领域研究的热点问题。

常见的硬件优化实现有如下几种方式:(1)串行方式。将轮函数展平,每轮对应一级组合逻辑,11轮迭代过程直接相连,前一级输出作为次一级的输入,每一个时钟周期均可完成一个分组处理;(2)迭代方式。各轮迭代只用一个对应轮函数功能的组合逻辑实体实现,每11个时钟周期完成一个分组处理;(3)流水线方式。用于提高系统工作时钟周期的流水线技术,一般仅在局部使用,或是与串行方式并用,可提高工作时钟频率,使其满足极大带宽的应用要求;(4)轮内实现流水线。在轮函数对应实体中插入寄存器,将一轮运算分至多个逻辑段完成,每个时钟周期仍能完成一个数据分组处理。

以上AES算法实现方式各有优缺点,但总体来说缺乏灵活性。当前应用于嵌入式系统的AES加密模块在灵活性、资源占用上还不是很理想。在对常用优化方法进行研究后,本文针对嵌入式系统设计一种AES加密IP核、实现低资源占用、高性能要求、32位数据位宽、且能方便进行并行连接,实现数据位宽扩展。

2 IP核设计

2.1 系统架构设计

IP系统分为时序控制、密钥处理、数据处理三个主要单元,其系统结构如图2所示。系统的工作模式分为闲置模式、密钥输入模式、单轮加密模式及连续加密模式。复位后系统处于闲置模式,单轮加密模式可以直接切换为连续加密模式,而连续加密模式需进入到闲置模式至少一个时钟周期后才可切换到单轮加密工作模式。

密钥处理单元在系统进入密钥输入模式后的连续4个时钟周期从数据输入端口读入总共128位密钥数据,在第5个时钟周期到来时完成第一轮密钥的计算,然后系统返回闲置模式。在加密模式中密钥处理单元按算法需求实时计算各轮密钥,并按32位为一组输出,与数据通道

- Linux嵌入式系统开发平台选型探讨(11-09)

- 嵌入式系统中文输入法的设计(03-02)

- 基于MPC755的嵌入式计算机系统设计(05-10)

- WinCE下光电编码器的驱动程序设计(04-12)

- 为什么嵌入式开发人员要使用FPGA(05-13)

- VxWorks几种常用的延时方法介绍(05-16)