液晶驱动MAX7232BF介绍及与单片机的硬件连接

MAX7232BF为串行输入4位数据、2位小数点和4位地址;输出为10位数据加20个独立小数点,数据输出代码为BCD码,每一位的2个小数点都在COM3上。可以直接与微处理器连接。

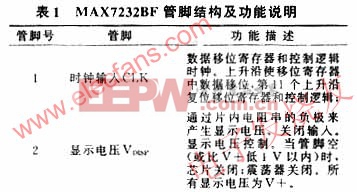

1 管脚结构及说明

MAX7232BF具有双列直插式40管脚封装和四边形式44脚封装。现以40脚封装的通用形式介绍其管脚结构及功能;44脚封装的形式类似,只是有部分管脚为空(NC),以及其他管脚号与其功能相对40脚有些差异。如表1所示。

2 动态显示驱动时序

由于LCD显示驱动信号与LED显示驱动信号不大相同,因而不能简单地在动态显示驱动方式的LCD电极上加高电平或低电平,否则显示会出现混乱。另一方面,LCD两电极间不能有直流电压,即两电极驱动信号的平均值应该为0。因此,LCD显示驱动信号需要采用偏压法,常用的偏压法有1/2偏压、1/3偏压、1/4偏压和1/7偏压等。MAX7232BF驱动信号采用1/3偏压来进行动态扫描驱动,扫描信号从背电极输出,显示信息从笔段电极输出。

3 译码选择格式

MAX7232BF输入4位数据、2位小数点和4位地址的二进制数据,他们的组合不同,产生的输出形式也各不相同。下面将分别讨论各种组合的译码格式,根据不同的显示需要,选择其中不同的编码组合来产生需要的显示格式。

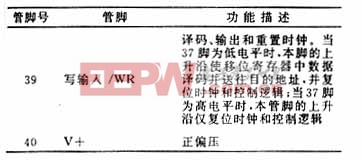

3.1 小数点译码输出格式

小数点控制输入2位,由此产生4种不同的组合,根据显示的需要可选择其中任一种格式,译码格式如表2所示。

3.2 数据译码输出格式

数据控制输入4位二进制数据,共形成16种输出格式,由于MAX7232BF输出为BCD码,只需要1~9共9位数字,另外还有1个不输出控制,其他6位不用。

3.3 地址译码输出格式

MAX7232BF最多可输出10位数据,由4位输入二进制地址数据来控制。将这4位数据译码为16位,其中前10位选择输出位的地址,后6位无效。

4 MAX7232BF的工作时序

MAX7232BF有3种输入时序:

第1种是用来输出10位数据(最大值,可以小于10位)和20个独立的小数点;

第2种是用来输出10位数据(最大值,可以小于10位)但不输出任何小数点;

第3种是用来输出10位数据(最大值,可以小于10位)但只输出右边10个独立的小数点(AN2)。

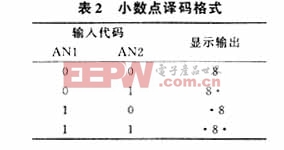

为了使设计的液晶显示器的显示功能尽量强大,不仅要在硬件上保证功能强大,在软件上也要使硬件的最大功能尽量发挥出来,所以在时序上要选择第1种时序,使2个小数点都可以显示,在此,只读第1种时序。图1为这种输入方式的输入时序。

如图1所示,其数据输入时序依次为:AN1→AN2→BD0→BD1→BD2→BD3→A0→A1→A2→A3,要求在时钟脉冲的上升沿时,按顺序输入这10位数据,他与时钟脉冲配合进行数据输入。在每个时钟脉冲的上升沿,MAX7232BF自动将数据输入线上的数据读入,因此,每个时钟脉冲都要输入一位数据,不允许在写期间停止若干周期,直到写控制线变为低电平为止。

另外还有写输入线与数据允许输出线的相互关系,以及通过他们来控制数据输入的原理及过程。当数据允许输出为高电平时,写输入线写脉冲的上升沿将会触发复位移位寄存器和控制逻辑,从紧接着的时钟脉冲上升沿开始读入数据;在数据允许输出保持高电平时,MAX7232BF正在读入数据时,若再有一个写输入脉冲,那么再次复位移位寄存器和控制逻辑,MAX7232BF重新开始读入数据;当数据允许输出为低电平时,写输入线的写脉冲上升沿将使数据允许输出变为高电平,二者共同作用使输入的数据译码、锁存入输出缓冲器中,并复位移位寄存器和控制逻辑,准备读入下一个数据。

5 MAX7232BF与单片机之间的硬件连接

采用89C51单片机的P1口作为控制显示器输入部分,利用其P1.2, P1.1和P1.0共3根控制线分别控制MAX7232BF的时钟输入、写控制输入以及数据输入;考虑到不同编程方式的需要,有些要利用 MAX7232BF的数据允许输出线的输出信号作为选择条件的要求,可以利用P1.3作为MAX7232BF的输出允许线的接收端。

6 软件编程

本文给出显示的子程序,子程序如下:

7 结 语

采用MAX7232BF作为液晶驱动,并以1/3时间分割法的方式驱动液晶显示器,用来代替并行显示器,以减少传输线的数目、提高显示器的寿命,以前极少见过用MAX7232BF作为液晶驱动的论述。本文对MAX7232CF和MAX7234系列也有参考意义。MAX7232CF与MAX7232BF 的区别在于MAX7232CF一个小数点在COM1上,而另一个在COM3上。MAX7234为串行输入6位数据(ASCII码),3位地址,输出为5个字符,但没有独立的小数点。

硬件 连接 单片机 介绍 驱动 MAX7232BF 液晶 相关文章:

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)