基于OMAP-L138的数字示波器微处理器硬件设计

面等。

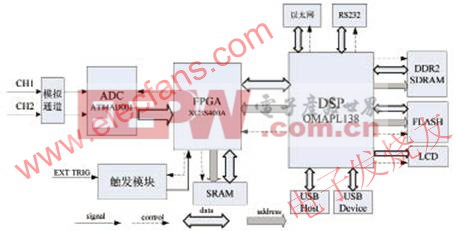

基于OMAP-L138的示波器硬件系统结构图如图2所示:

图2 数字示波器系统结构图

本设计中,被测信号进入模拟通道调理后送入ADC,ADC对模拟信号采样、量化后,进入FPGA数据流降速和数据同步处理,然后根据存储深度要求选择存入 FPGA内部FIFO或者存入片外SRAM,待FPGA内部FIFO或者片外SRAM满标志有效后,DSP读取采样数据存入DDR2 SDRAM,并完成一系列复杂的处理和运算,如FFT、插值和滤波等,再存入在DDR2内拓展的显示存储区,待需要显示时再由DSP读取显存中的数据通过内部集成的LCD控制器采用DMA方式将数据送到LCD显示,完成一次采集过程。

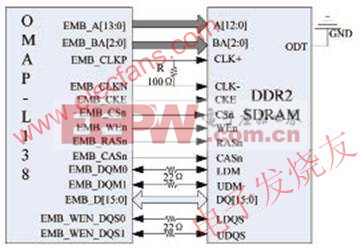

OMAP-L138与DDR2的接口电路设计

OMAP- L138内部集成的DDR2/Mobile DDR控制器可外接工作频率150MHz的DDR2 SDRAM或者工作频率133MHz的Mobile DDR。本设计采用DDR2 SDRAM作为系统后级波形数据缓存器。较之SDRAM,DDR2 SDRAM不仅读写速度可大幅提高,存储容量更是得到极大扩展,示波器因而能够存储更多波形数据并观察到更多的波形细节,提高示波器对复杂信号和瞬态信号的捕获概率。本设计的DDR2 SDRAM选用镁光公司的DDR2 800内存颗粒,型号为MT47H64M16,容量为1Gbit,核心工作电压为1.8V,核心工作频率为400MHz,由于OMAP-L138内部的 DDR2控制器最高工作频率为150MHz,所以此系统中DDR2需要降频使用。OMAP-L138与DDR2的接口连接示意图如图3所示:

图3 OMAP-L38与DDR2的接口连接示意图

DDR2 的信号线包括时钟、数据和命令三部分。本设计由DDR2控制器提供差分时钟CLK+和CLK-给DDR2,,差分时钟之间并接一个100Ω的匹配电阻,用以消除时钟的毛刺并限制驱动电流;数据部分主要完成数据传输工作,包括数据线DQ[15:0]、数据同步信号DQS(本设计LDQS对应数据线低八位,UDQS对应数据线高八位)、数据信号屏蔽线DM(在突发写传输时屏蔽不存储的数据,LDM对应数据位低八位DQ[7:0],UDM对应数据线高八位 DQ[15:8]),本设计在DQS信号和DM信号上串接一个22Ω的电阻,起抗干扰和滤波作用,提高信号质量;命令部分包括行地址选通信号RASn、列地址选通信号CASn、写使能信号WEn、片选信号CSn、时钟使能信号CKE以及芯片内部终端电阻使能ODT,主要完成寻址、组成各种控制命令以及内存初始化工作。本设计由于DDR2控制器内没有终端电阻,因此将DDR2 SDRAM的ODT信号直接接地使DDR2芯片内的终端电阻无效。

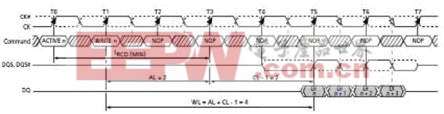

DDR2的读、写时序图分别见图4和图5:

图4 DDR2的读数据时序图

图5 DDR2的写数据时序图

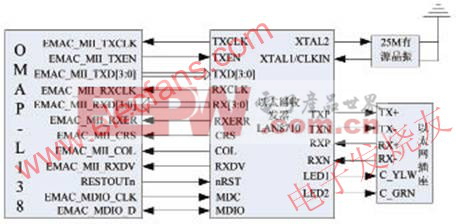

以太网的接口电路设计

用示波器测量电信号时,信息和测量结果便捷的保存和共享变得日益重要。若数字示波器提供以太网接口,开发人员就可以方便地将测量数据和结果通过网络共享,实现远程调试;也可以将波形数据通过网络上传到PC机上,在PC机上实现波形数据的处理、分析和显示。

OMAP-L138内部集成的以太网控制器(EMAC)支持IEEE802.3标准,支持10Base-T和100Base-T两种以太网标准,有全双工和半双工两种工作模式可供选择,提供了MII和RMII两种以太网接口。

选用LAN8710以太网收发器,该以太网收发器提供MII和RMII两种以太网接口。本设计采用MII接口实现LAN8710与EMAC的互联。MII接口包括一个数据接口,一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道有4根数据线、时钟和控制信号,其中管理接口是双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。管理接口的时钟MDC由EMAC提供,最高可达 8.3MHz;数据信号MDIO是双向接口,与MDC同步,控制收发器并从收发器收集状态信息。可收集的信息包括链接状态、传输速度与选择、断电、低功率休眠状态、TX/RX模式选择、自动协商控制、环回模式控制等。

以太网接口连接示意图如图6所示:

图6 以太网接口连接示意图

本设计采用外接25M有源晶振为以太网收发器提供时钟输入,当配置为100Mbit/s的数据传输速率时,LAN8710提供给EMAC 25MHz的发送时钟TXCLK和接收时钟RXCLK;当配置为10Mbit/s的数据传输速率时,25MHz时钟输入经LAN8710内部PLL分频 10倍后得到2.5MHz的收、发数据时钟送给EMAC。发送数据总线TXD[3:0]和接收数据总线RXD[3:0]分别在发送时钟TXCLK和接收时钟RXCLK的上升沿被触发。当选择半双工工作模式时,网络冲突监测信号COL若检测到网络出现数据发送冲突,该信号会自动置位报警。载波感应信号CRS 在网络处于繁忙状态时,会自动置位并告知EMAC。若在接收的帧中发现错误,接收数据错误标志信号RXERR会置位,并持续一个或几个RXCLK时钟周期。

结论

本设计有以下

硬件 设计 微处理器 示波器 OMAP-L138 数字 基于 相关文章:

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)