基于高分辨率乘法DAC的交流信号处理

| 产品型号 | 电源电压 | BW (–3-dB) | 压摆率 | 最大VOS | 最大IB | 封装 |

| AD8065 | 5 至 24 | 145 | 180 | 1500 | 0.006 | SOIC-8, SOT-23-5 |

| AD8066 | 5 至 24 | 145 | 180 | 1500 | 0.006 | SOIC-8, MSOP-8 |

| AD8021 | 5 至 24 | 490 | 120 | 1000 | 10,500 | SOIC-8, MSOP-8 |

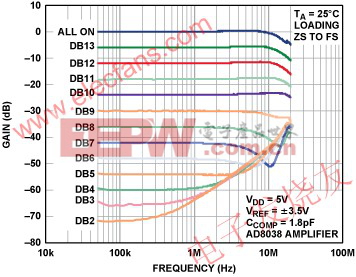

| AD8038 | 3 至 12 | 350 | 425 | 3000 | 750 | SOIC-8, SC70-5 |

| ADA4899 | 5 至 12 | 600 | 310 | 35 | 100 | LFCSP-8, SOIC-8 |

| AD8057 | 3 至 12 | 325 | 1000 | 5000 | 500 | SOT-23-5, SOIC-8 |

| AD8058 | 3 至 12 | 325 | 850 | 5000 | 500 | SOIC-8, MSOP-8 |

| AD8061 | 2.7 至 8 | 320 | 650 | 6000 | 350 | SOT-23-5, SOIC-8 |

| AD8062 | 2.7 至 8 | 320 | 650 | 6000 | 350 | SOIC-8, MSOP-8 |

| AD9631 | ±3 至 ±6 | 320 | 1300 | 10,000 | 7000 | SOIC-8, PDIP-8 |

结论

自首款CMOS M-DAC问世以来的近40年间,相关器件不断更新换代,许多新的功能特性层出不穷,性能持续提升,成本和尺寸则大幅缩减。我们的高分辨率、14位/16位电流输出DAC产品系列AD55xx的最新性能改进

- DSP在交流异步电动机变频调速中的应用(10-04)

- 基于MSP430的变频伺服系统设计(05-05)

- 多路交流异步采样及DSP软件校准技术(10-13)

- 基于ARM控制器LPC2214的税控收款机系统的设计与实现(06-04)

- 基于PLC和交流伺服的单轴控制系统(12-20)

- DSP交流伺服系统与CAN总线的通信设计(12-20)