基于Hyperlynx的DDR2嵌入式系统设计与仿真

在相关网站上下载该处理器和该型号内存的IBIS模型。根据JESD79-2C DDR2 SDRAM SPECIFICATION的说明要求,可以知道地址/命令/控制信号以及DQS差分对或时钟信号的DC和AC工作标准对DDR2-800要求如表1所示。根据上述指标可以得出眼图的数据,然后设置叠层编辑器来设置特性阻抗值,导入CPU以及存储器的IBIS模型,根据实际设计设置网络中上拉电阻以及滤波电容的实际值,可以读出有效特性阻抗值Z0=54.3 Ω,以及每位周期的值。因为信号频率为400 MHz,所以每位周期设置为1.25 ns。 从图3眼图可以看出,信号在不同DIMM内部和外部的信号质量是不同的,在没有端接电阻以及布线、阻抗调整的情况下,运行400 MHz的频率信号十分差,眼图的宽度、高度、上升斜率等关键指标都不符合JEDEC对DDR2-800的DC/AC规范。 同理,可以对重要的差分信号和时钟信号进行仿真。而DDR2中新增加的ODT(On Die Termintation)功能在仿真中可以得到体现。通过不设置以及设置ODT的值,可以直观地在眼图以及客观地在仿真结果数据一栏中得出合成差分信号的质量。图5为差分信号的仿真结果眼图。 通过眼图和数据,可以确定最优差分阻抗和ODT值的设置。 高速信号的PCB优化设计,可以在PCB的设计阶段,运用Hyperlyxn仿真工具和IBIS驱动模型,对高速信号设计中的关键信号进行完整性仿真和时序分析、EMI仿真、分析和优化,可以发现PCB制好后调试中可能出现的问题,从而可以节约成本、缩短产品的设计时间。

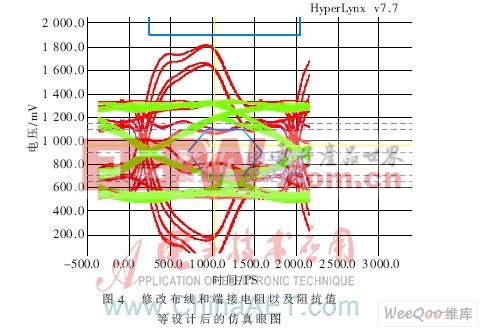

图4为修改Layout布线和端接电阻以及阻抗值等设计后的仿真眼图,从图4可以明显直观地看到,修改之后信号状况大大改观,而且可以直接读出眼宽、高电平值、低电平值、采样眼宽等信号眼图的重要数据,以便于确定硬件和PCB设计。

设计 仿真 系统 嵌入式 Hyperlynx DDR2 基于 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)