C8051F单片机实验系统设计

2.2 液晶显示模块

液晶显示器(LCD)以其微功耗、体积小、显示内容丰富、超薄轻巧等诸多优点,在便携式仪表和低功耗应用系统中得到越来越广泛的应用。

LCD可分为段位式LCD、字符式LCD和点阵式LCD。其中,段位式LCD和字符式LCD只能用于字符和数字的简单显示,不能满足图形曲线和汉字显示的要求;而点阵式LCD不仅可以显示字符、数字,还可以显示各种图形、曲线及汉字,并且可以实现屏幕上下左右滚动,动画功能,反转,闪烁等功能,用途十分广泛。

点阵式LCD分为带汉字字库和不带汉字字库两种,带字库LCD若要显示汉字只要传给汉字内码,而不带字库LCD显示汉字时要先求出汉字字模,然后跟显示图形一样显示汉字。

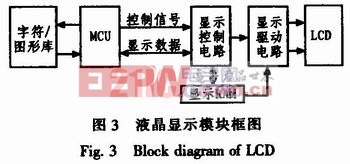

本开发系统采用博控公司生产的NS240*128A点阵图形型LCD,不带中文字库。由于液晶显示器是典型的慢速设备,如果直接与高速的单片机相连时,会浪费大量的时间,可以考虑在单片机和液晶显示器中间加入FPGA,由FPGA直接驱动和控制液晶显示器。液晶显示模块框图如图3所示。

单片机将字库/图形库内的图形或文字数据以及这些数据在液晶上所显示的位置信息传送给由FPGA芯片构成的液晶控制IP核。由于LCD是慢速设备,单片机发送至LCD控制器的显示数据信息的速度通常大于LCD显示更新速度,因此需将这些数据和信息送入数据存储器中缓存。由于FPGA芯片的片内RAM容量有限,系统中外扩了1片RAM作为显示数据缓冲器。由FPGA芯片构成的显示控制IP核需读取外扩显示RAM中的数据,再通过显示驱动电路按字节送至LCD进行显示:因此在所设计的显示驱动电路中设计了一个双端口RAM,既能将显示数据缓存器中的显示数据写入双端口RAM,同时又能将双端口RAM中的数据读出,再将数据送至LCD数据接口。

2.3 SRAM模块

C8051F020内部有位于外部数据存储器空间的4 096字节的片上RAM,还有外部数据存储器接口EMIF,可用于访问片外存储器和存储器映射的I/O器件。外部数据存储器接口EMIF可配置到低I/O端口P0~P3,也可配置到高I/O端口P4~P7。而且,既可以配置为数据、地址复用方式,也可以配置为非复用方式。若要节省端口I/O,可采用数据、地址复用方式,能节省8根端口线,但是速度较慢,若要提高速度,则可

以采用非复用方式。

2.3.1 配置外部存储器接口的步骤

1)将EMIF选到低端口(P3~P0)或选到高端口(P7~P4)。

2)选择复用方式或非复用方式。

3)选择存储器模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器)。

4)设置与片外存储器或外设接口的时序。

5)选择所需要的相关端口的输出方式。

在本系统中考虑到(28051F020单片机的PO~P3口大部分为功能复用引脚,为使单片机的资源得到最大的开发,将单片机的高端I/O口,即P4~P7接入FPGA,并通过FPGA对RAM进行访问。将单片机配置为高端口(P4~P7)、地址/数据总线分时复用方式,FPGA控制RAM的片选、读/写等操作,其中注意FPGA、单片机、RAM的时序统一问题。

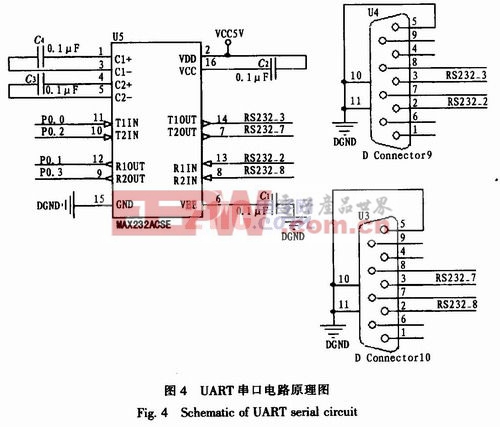

2.4 UART串口

UART是一种通用串行数据总线,该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来与PC进行通信,包括与监控调试器和其他器件,如EEPROM通信。

UART首先将并行数据转换成串行数据来发送。消息帧从一个低位起始位开始,后面是若干数据位,一个可用的奇偶校验位和一个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。在接收过程中,UART从消息帧中去掉起始位和结束位,对进来的字节进行奇偶校验,并将数据字节从串行转换成并行。UART也产生额外的信号来指示发送和接收的状态。例如,如果产生一个奇偶错误,UART就置位奇偶标志。

C805lF020单片机中有两个增强型串行口:UART0和UARTl。所谓增强型是指,这两个串口都具有帧错误检测和通信地址硬件识别功能。它们都可以工作在全双工异步方式或半双工同步方式,并且支持多处理器通信。开发板外扩两个增强型UART串口,实现单片机与PC机、单片机和单片机之间的通信。其电路连接如图4所示。

2. 5 A/D和D/A模块

C8051F020有一个片内12位ADC(ADCO)和一个8位ADC(ADCl),通道输入多路选择开关和可编程增益放大器。

ADC的电压基准可以在模拟电源电压(AV+)和一个外部VREF引脚之间选择。A/D转换有4种启动方式:软件命令、定时器2溢出、定时器3溢出和外部信号输入。这种灵活性允许用软件事件、外部硬件信号或周期性的定时器溢出信号触发转换。转换结束由一个状态位指示,或者产生中断(如果中断被使能)。在转换完成后,12位或8位转换结果数据字被锁存到两个特殊功能寄存器中。这些数据字可以用软件控制为左对齐或右对齐。

C805lF020内部有两个片内12位电压方式数/模转换器(DAC)。每个DAC的输出摆幅均为0 V到(VREF-1LSB),对应的输入码范围是Ox000到OxFFF。C8051F020的VREF引脚可以由内部电压基准或一个外部源驱动。如果使用内部电压基准,为了使DAC输出有效,该基准必须被使能。

本文设计了利用A/D和D/A模块进行简单的语音信号的存储和回放,基本思想是将模拟语音信号经过前置放大和滤波电路的处理,通过模数转换器A/D转换成数字信号,再通过单片机控制存储在存储器中,回放时,由单片机控制将数据从存储器中读出,然后通过数模转换器D/A转换成模拟信号,经放大在扬声器或耳机上输出语音。音频前置放大和滤波电路如图5所示。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)