AMBE2000在语音通信中的设计

无论是在人们的日常交流,还是在航空、航天等高科技领域,语音通信都是不可或缺的。根据奈奎斯特理论,要想不失真地重构语音信号,采样频率不能低于40 kHz,按8位采样精度计算,语音数据量也有320kbit/s,占用的数据带宽多,严重破坏通信系统(特别是无线通信系统)的通信性能。因此需要寻找合适的语音编码方法,将语音数据率压缩到理想状态,使其能够占用较少的带宽,实现理想的通信效果。

笔者设计的无线通信系统利用DVSI公司语音编解码芯片AMBE2000实现了低带宽、双工的数据与语音同传,语音通信自然可懂。

AMBE2000

MBE(多带激励)语音编码技术是一种具有高语音质量和强鲁棒性的低速率语音编解码技术。这种方法在频域中按基音各谐波频率,将一帧语音的频谱划分为多个频带,对每个频带作清、浊音判决。对浊音带,以基音为周期的脉冲序列作为激励信号;对清音带,则以白噪声作为激励信号。总的激励信号由各带激励信号相加构成。用该激励信号激励声道滤波器,最终合成出具有较高自然度的语音。MBE模型使合成语音谱与原语音谱在细致结构上能拟合得很好,因此在低比特率的情况下,其合成语音的音质依然能保持较高的自然度。其改进的AMBE算法成为国际移动卫星组织和移动卫星通信的语音编码标准。

AMBE2000采用AMBE编解码技术,是一种高性能、低功耗的单片实时语音压缩解压芯片,其压缩率可在2kbit/s~9.6kbit/s范围内由硬件、软件调节,且具有FEC(前向纠错)、VAD(语音激活检测)功能和DTMF信号检测功能,当速率在4.0kbit/s以上时,可得到接近长途电话的话音质量;当速率为2.0kbit/s时,仍然具有较高的可懂度和自然度。因此可广泛应用于卫星通信、数字移动通信、保密通信、语音邮件等方面。

AMBE2000的主要特性包括:具有高品质的语音质量,压缩数据率可在2kbit/s~9.6kbit/s范围内调节,步进50bit/s; 纠错率范围为50bit/s~7.2kbit/s;低功耗、低复杂度;具有语音激活检测VAD功能、回波抵消功能和舒适噪声CNI产生功能;可变速的FEC功能; DTMF信号检测和产生功能等。

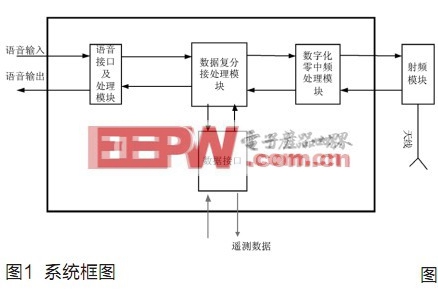

系统设计

系统实现语音与数据的无线遥测同传,系统框图如图1所示。其主要组成部分为:语音接口与处理模块、数据接口模块、数据复分接模块、中频处理模块、射频模块和天线。其中,语音接口与处理模块主要采用AMBE2000实现,数据接口采用FIFO实现,数据复分接和中频处理采用FPGA实现,完成软件无线电功能。

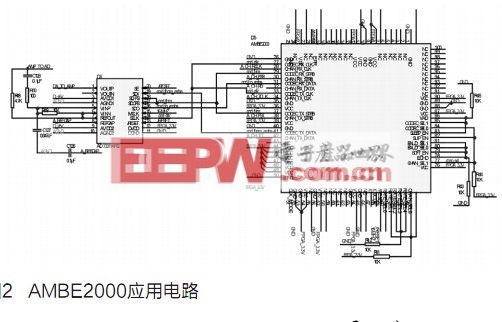

AMBE2000应用电路

图2所示是系统中AMBE2000的应用电路。图中,AMBE2000选择的引脚接法将其设置为语音位为1位的被动无帧格式、码速率为4kbit/s、外部输入时钟模式、AD/DA为AD73311模式、滑动补偿功能有效,其EPR引脚用来输出数据包就绪指示信号。

工作模式设置

AMBE2000与外部接口为串行接口,串口时钟速率最高为2.048MHz,大约每20ms生成一个压缩数据包。可设置为主动和被动模式,在被动模式,所有接口控制信号由外部输入;在主动模式,CHAN_TX _STRB由AMBE2000输出,其他信号由外部输入。

AMBE2000与外部的接口数据格式分为两种:有帧格式,无帧格式。

本系统将AMBE2000的输入引脚77、75置为高电平,相应的工作方式为被动无帧格式。

码速率设置

AMBE2000的初始码速率设置必须通过硬件引脚RATE_SEL[4-0](pin74-70)设置,器件复位工作后,可通过软件数据包设置。

在无帧格式情况下,只需要发送数据位,译码端约需要15包数据(300ms)进行输入数据流同步。每个字中只有1-4位传输语音,由引脚BAUD_SEL1(pin 81) 、BAUD_SEL0(pin 80)控制。

本系统设置RATE_SEL[4-0]为10001,对应码速率为4kbps;将引脚80、81置为低电平,每字只有1位语音数据。

时钟

AMBE2000的工作时钟频率为16.384MHz,有两种提供方式:外部TTL/CMOS时钟源、晶振,由引脚CLOCK_MODE(pin 51)指定,时钟输入端为X2/CLKIN(pin68)、X1(pin67)。(1)CLOCK_MODE=0,外部TTL/CMOS时钟源作为时钟输入,连接方式见图3。

(2)CLOCK_MODE=1,16.384MHz晶振作为时钟输入,连接方式见图4。 要求C1、C2与晶振距离AMBE2000尽可能近。

本系统采用方式(1),由FPGA提供16MHz输入时钟。

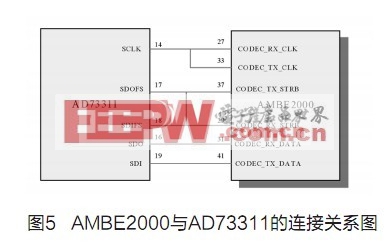

AD/DA

通过芯片引脚CODEC_SEL1(PIN 85)、CODEC_SEL0(PIN 84)进行A/D-D/A接口配置,本系统将引脚85、84设置为01,即AD73311配置。AMBE2000与AD73311的连接见图5。

工作流程

复位后,等待EPR(pin 20)出现下降沿,表明译码数据包准备好,读取数据包,以后约每隔20ms读一包数据。

本系统设置每字的语音位为1,复位并等待EPR(pin 20)出现下降沿后,根据设定的码速率固定每次读取一个

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)