Altera器件时间匹配问题的解决方案

时间:12-10

来源:互联网

点击:

还可以通过在MAX+PLUSII中仔细地分配资源,来提高设计的可靠性。在MAX器件中通过PIA的信号将会有时间延时。为消除这种延时,可以在MAX+PLUSⅡ中进行团体分配,也就是将计数器邻接的位安排在同一个LAB中的诸宏单元内。

4 结束语

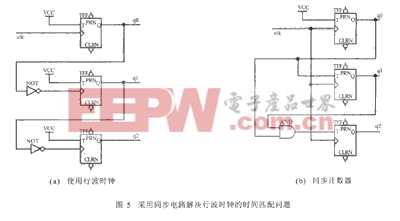

在组合电路中,从信号输入到稳定输出需要一定的时间。由于从输入到输出的过程中,不同通路上门的级数不同,或者门电路平均延迟时间的差异,使信号从输入经不同通道传输到输出级的时间不同,由于这个原因,就产生了毛刺。这是一个普遍性的问题。本文对解决毛刺的方法作了一个总结,有利于大家快速、准确设计稳定的集成电路。在这个问题上,AHDL语言比VHDL语言要直观、易于理解。从宏观上看,要解决Altera器件设计中的时间匹配问题,要使用同步设计。采用同步电路设计也可以使电路免受外部因素影响(如硅处理工艺和温度变动)而造成的时间匹配问题。

- 嵌入式系统的VxWorks安全性问题研究(11-06)

- DSP编程过程中的几个关键问题的研究(06-05)

- 教你构造一个51单片机的实时操作系统(08-22)

- DSP开发中值得注意的问题(02-16)

- 基于DSP编程的几个关键问题(03-26)

- 调试前的组网故障问题总结(12-19)