Altera器件时间匹配问题的解决方案

时间:12-10

来源:互联网

点击:

1 引言

Altera的 MAX+PLUSⅡ可编程逻辑开发软件,提供了一种与工作平台、器件结构无关的设计环境,深受广大电子设计人员的喜爱。但设计人员都会遇到Altera器件设计中的时间匹配问题,本文对这个问题展开了讨论,对电路中短时脉冲波形失真的所谓毛刺现象进行了研究,并提出了解决的办法。

2 消除毛刺

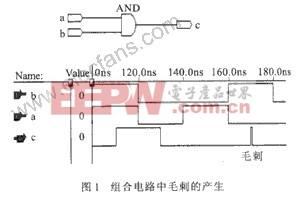

某个事件成功的条件不分先后顺序,只要满足成功的组合需求,此事件就算成功,此种逻辑关系就是组合逻辑。我们在使用Altera器件进行组合逻辑的设计时,常遇到短时脉冲波形失真,即毛刺问题(见图1)。在组合电路中,两输入AND门是最简单的电路,从MAX+PLUSⅡ中的 Timing Analyzer的Delay Matrix 中可得知a=11.1ns,b=8. 1ns。假定AND门内部的延时时间为0.2ns,那么 a的延时+ AND内部的延时(0.2ns)=11.1ns,a的延时为10.9ns; b的延时+AND内部的延时(0.2ns)=8.1ns,b的延时为7.9ns。由于 a和b的延时时间不相等,所以当a从1变为0,同时b从0变为1时,输出结果c产生了毛刺。

|

Altera器件结构有许多特点,使你在设计时具有较大的灵活性,但是,它可能会引入附加的时间延时。另外,复杂可编程逻辑器件中具有称作逻辑阵列块(LAB)的小型、高性能、灵活阵列模块,还有称作可编程连线阵列(PIA)的专用可编程网络,MAX的结构通过PIA来连接LAB,保证其100%的内部连接布通率。每个LAB中的逻辑扩展项都提供附加的逻辑资源给LAB中的任何一个宏单元。但是,所有来自宏单元和扩展项的信号经过PIA时都必然引入时间延时,从而可能在组合逻辑的输出端产生毛刺。对于怎样消除毛刺,我们作了以下探讨。

2.1 软件修改输入端子的延时时间

一些软件(如Xilinx公司)提供的方法是通过修改输入端子的延时时间,来解决毛刺问题的。如图1中,我们用软件把 b输入端子的延时时间改为10.9ns,这样a与 b的延时时间相等,就消除了输出端c的毛刺。它的优点是能快速解决问题,这是设计中最简单实用的方法。

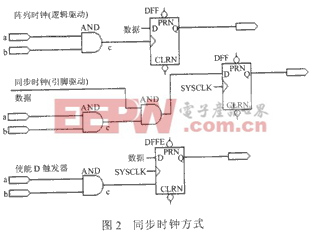

2.2 修改电路

通过修改定义时钟信号的复杂逻辑,将其转换成同步时钟方式就可以避免毛刺出现。同步时钟是采用单一的引脚驱动的系统时钟,而不是异步的(逻辑驱动的)时钟,见图2。只要可能就应尽量采用同步设计,可以避免定时关系发生问题。另外,同步设计也可以改善电路的在线性能,减少调试时间和提高电路的可靠性。在同步时钟方式中 c信号是D触发器输入的一部分,而且时钟是由引脚驱动。这个电路称作寄存器使能电路, MAX+PLUSⅡTTL宏功能库中提供了一种可以实现这种类型电路的D触发器DFFE(见图2)。

|

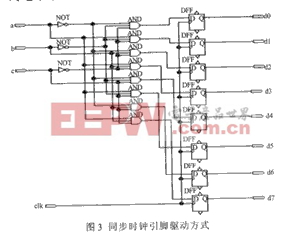

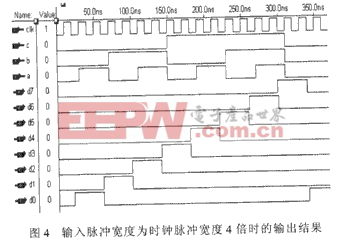

对于三到八译码器而言,用a、b、c表示输入引脚,d0、d1、d2、d3、d4、d5、d6、d7 表示三到八译码器的输出引脚。对该设计项目进行编译后模拟仿真,这时非常容易从模拟仿真出来的波形上看到出现了毛刺。如采用同步时钟(引脚驱动)方式,就可以消除毛刺。要注意的一点是建立和保持时间(Setup/hold time )是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间Set up time。如不满足Setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。hold time不够,数据同样不能被打入触发器。我们选用a端的输入脉冲宽度是时钟脉冲的四倍,这样D 触发器就可以正常动作,输出结果是正确的,见图3、图4。如果我们一定要使输入脉冲等于输出脉冲的宽度,就要使输入脉冲的高电平与时钟脉冲的高电平错开,保证D触发器能工作。

|

|

2.3 重新设计电路

毛刺是信号趋于稳定前不必要的开关动作,使每个时钟沿改变了寄存器间组合逻辑的输入。对每个节点而言,不同的输入路径有不同的延时,这将多次改变状态。节点上的毛刺多少与该节点的逻辑深度,也就是节点至最初输入的逻辑门个数有关。到达节点的逻辑锥体越深、越宽,毛刺也越多。降低逻辑深度,减少逻辑锥体的开关输入可减少这类毛剌。时序驱动合成以及逻辑单元的合理映射能减少逻辑级的数量。

如果一个计数器的输出端接一个组合电路,这个组合电路的输出端产生了毛刺,最好的解决方法是重新设计电路,只要在这一时刻改变计数器输出端子的输出顺序,就可以消除下一级组合电路输出端的毛刺。例如,在下面程序中,在这一时刻改变q0、q1、q2输出顺序,就能解决计数器输出所接的组合电路输出端毛刺的问题。

subdesign modcount

(clk,reset:input;

q[2..0]

utput;

utput; )

variable

counter3:machine of bits(rr[2..0])

with states(r0=B101, --换成r5的输出

r1=B100, --换成r4的输出

r2=B000, --换成r0的输出

r3=B001, --换成r1的输出

r4=B011, --换成r3的输出

r5=B010, --换成r2的输出

r6=B110,

r7=B111);

begin

q[ ]=rr[ ];

counter3.reset=reset;

counter3.clk=clk;

CASE counter3 IS

when r0=>counter3=r1;

when r1=>counter3=r2;

when r2=>counter3=r3;

when r3=>counter3=r4;

when r4=>counter3=r5;

when r5=>counter3=r6;

when r6=>counter3=r7;

when r7=>counter3=r0;

END CASE;

End ;

3 行波时钟时间匹配问题

行波时钟是计数器通常使用的一种时钟方式,而使用行波时钟是可能引起潜在时间匹配问题的另一个因素。所谓行波时钟是指一个寄存器的输出为另一个寄存器产生时钟,而不是使用一个公共的系统时钟。如果仔细设计,行波时钟可以像全局时钟一样可靠工作,但是行波时钟使得与电路有关的定时计算变得很复杂。行波时钟在行波链上各寄存器时钟之间将产生较大的时间偏移,并且会超出最坏情况下的建立时间、保持时间和电路中时钟到输出的延时,使系统的实际速度下降。在图5(a)中使用行波时钟所示电路的时钟周期依赖于计数器最低位的变化沿计数器传播到最高位所花的时间,这个周期与计数器的位数有关。随着逐位进位计数器的位数增加,系统的速度将下降,为此可使用同步电路来解决这个问题,如图5(b)所示。当把异步计数器改成同步操作时,系统的速度由寄存器的建立和保持时间决定,而不是由计数器的位数决定。同步电路不需要使用附加的资源,就可以提高计数器的速度,并消除出现非法计数数值的可能性。

- 嵌入式系统的VxWorks安全性问题研究(11-06)

- DSP编程过程中的几个关键问题的研究(06-05)

- 教你构造一个51单片机的实时操作系统(08-22)

- DSP开发中值得注意的问题(02-16)

- 基于DSP编程的几个关键问题(03-26)

- 调试前的组网故障问题总结(12-19)