基于ARM920T设计的SMC接口研究与PC/104总线仿真

高位线.

2.2 AHB总线时序和SRAM 接口

AHB(Advanced High-Speed Bus)是EP93 1 5内部920T核与存储器、DMA,存储器等设备实现高速互联的系统总线.EP9315的AHB具有完善的多主控冲突仲裁能力,其典型工作频率可达100 MH。

静态存储控制器SMC(Static Memory Controller)与920T核心通过AHB互联,支持存储器的8/16/32位访问方式.SMC最多可提供8个组,每个组均可支持SRAM,ROM,FLASH EPROM 等存储器的访问,各组可以对数据总线宽度和速度等参数独立配置.图2描述了SRAM 读操作时序.

图中f删为CSn到RDn的延迟,最大值为3 ns;tDAs是RDn无效前的数据总线建立时间,最小值为12+tHcI tRDD 是RDn有效时间,典型值为t HcI K×(W ST1+ 2)。

HCLK是AHB总线的工作频率,该频率的高低直接影响系统全局性能,因此通常配置为上限100 MHz,此时相应周期£胁 为10 ns.WSTI用于控制sMc对SRAM/R0M 的访问速度,寄存器SMCBCR0—3, SMCBCR6-7 (地址0x80080000—0x8008001C)的第5-9位分别为相应各组的WST1.WST1的默认值为0xlF,即默认情况下SMC使用

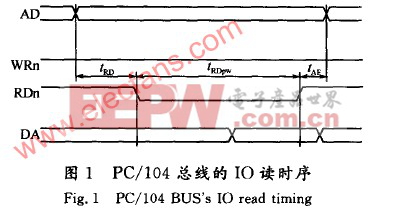

最低的访问速度,显然fRDD 为330 ns,小于PC/104总线中的500 ns(图1).

3 PC/104总线实现

3.1 总线驱动

在EP9315支持的各类总线接口逻辑中,SMC提供的SRAM/ROM 时序与PC/104总线最为接近.将外部设备所需的PC端口空间和存储器空间均映射至统一的虚拟空间中即可实现访问.

注意到PC/104总线使用标准TTL逻辑电平,而EP9315的处理器是3.3 V器件,在极端负载情况下无法保证系统稳定工作.TI的双电源总线收发器1T45,2T45,16T245等可用于实现电平转换,图3是1T45的引脚逻辑图.

地址总线及访问控制信号均由CPU驱动,外部设备始终处于被动接收状态,正确设定数据流向即可.

数据总线信号是时分双向传输的,为遍免出现总线冲突,必须保证除非CPU 透过该收发器对外设进行读访问,否则收发器的CPU 侧应始终处于高阻状态.为此,16T245等具有输出使能端的器件只需使输出无效即可,而对于无使能端的收发器则应使CPU侧处于输入状态(高阻).

确认CPU 已向兼容PC/104总线发起读操作的有效方法是检查RDn的下降沿是否发生.一旦RDn下降,应立即将收发器置成从外设流向CPU方向,且输出使能有效,并至少保持至RDn上升沿之后,以保证可靠读取.

3.2 端口映射

SMC的存储器分组片选信号CSn可作为高位地址线参加这址译码.任取CSi和CSj组用于兼容总线,即可分别实现O-0x3FFFFFF的独立存储器地址和IO端口地址.可用地址数量已经远超出XT系统中的1 M(存储器)和1 K(IO端口).

在Linux系统中,io.h文件中声明了函数iore—map(),用于将兼容总线上外部资源的物理地址映射到核心虚地址空间中.iounmap()函数用于取消ioremap()所做的映射.上述操作都应在设备驱动程序中执行.在外部资源成功映射到核心虚地址后,使用指向核心虚地址的指针就可访问相应设备资源,但显然这种访问方式与在X86平台下差异较大.

将兼容总线视为一个独立的字符设备,为其编写驱动程序,实现对指定偏移地址的读写函数,此处的偏移地址即对应PC/104总线中的物理地址 .

对inb(),outb()等X86平台下的常见的底层端口操作函数,可用宏替换的方式转由驱动中的相应读写函数实现.

3.3 总线时序控制

综合前文所述,尽管SMC的SRAM 访问时序非常接近PC/lO4总线,但是要实现高兼容性的PC/lO4,仍有两方面问题需要解决,一是SMC驱动的SRAM 读写速度远高于PC/104总线,二是为解决电平兼容问题引入的总线收发器,其数据流向和输出使能需要适当的控制.

以下VHDL代码根据SMC输出的RDn和WRn设置EIOR和EIOW 时序,并适时输出信号EXIDR,EXOE控制收发器数据流向和输出使能.

ECLK是频率为27 MHz是时钟脉冲.

If ECLK’EVENT and ECLK一‘1’then

if( )then __地址无效

EXoE 一:1’;

EXDlR 一‘1’;

EIOR 一‘1’;

rdreg 一0;

else

if rdreg 1 l then

rdreg 一rdreg+ 1;

EXOE 一‘0’;

else

rdreg 一0;

EXDIR 一‘1’;

EXoE 一‘1’;

end if;

if rdreg 2 or rdreg> 6 then

EIOR 一‘1’;

EIOW 一‘1’;

elsif rdreg一2 or rdreg= 3 then

if RDn一‘1’then

EIOR 一‘1’;

EXDIR 一‘1’;

elsif W Rn一‘1’then

EIOW 一‘0’;

EXDIR 一‘1’;

end if;

end if;

上述代码适当延迟了关闭双电源收发器的输出使能和数据流向重设时间,保

PC 104 总线 仿真 研究 接口 ARM920T 设计 SMC 基于 相关文章:

- VXWORKS内核分析(11-11)

- CE系统启动时自动运行应用程序(11-14)

- 基于MPC8250的嵌入式Linux系统开发(07-16)

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)