基于Blackfin DSP的TFT LCD液晶接口设计

TFT LCD液晶显示器与数码管和点阵液晶相比具有体积小巧、控制简单、可以显示丰富多彩的图像视频信息。文中以ADSP_BF532为例介绍了一种Blackfin DSP处理器与TFT LCD液晶显示器的接口设计,在Blackfin DSP的系统设计中具有一定的参考价值。

1 Blackfin DSP处理器与TFT LCD液晶屏简介

Blackfin DSP处理器是基于ADI公司和Intel公司联合开发的微信号架构(MSA)的一种16位定点DSP处理器,具有较强的数据处理能力,能够完成视频、图像、音频和通信数据的数字化处理等。同时还具有综合控制能力,单芯片即可完成通常由DSP+控制器完成的功能。Blackfin DSP处理器可广泛应用在各种嵌入式设备、仪器中,完成系统控制和数据处理。

PPI(Parallel Port Interface)接口是Blackfin DSP处理器的并行数据接口,主要用于数据的高速传输。它包括16位数据线,3个同步信号和一个时钟信号。PPI接口直接与DMA通道整合,数据传输宽度可灵活配置,支持8位、10~16位等多种数据宽度。PPI的工作模式有两种:通用模式(GP模式)和ITU-656模式,其中通用模式下可方便地与数字液晶屏连接。

Blaekfin DSP处理器的DMA传输可以是内部与外部存储器之间,也可以是内部或外部存储器与SPI口、SPORT口、UART口、PPI口之间。

Blackfin DSP处理器的DMA传输可基于描述符配置,也可基于寄存器配置。基于描述符的DMA传输使用存放在存储器内的一组参数来初始化一个DMA传输。基于描述符的DMA传输允许多个DMA序列链接在一起,一个DMA传输完成后紧接着进行下一个DMA传输。基于寄存器的DMA传输允许处理器通过对控制寄存器编程来启动一个DMA传输。一次DMA传输完成后,可以用原来设置的值自动更新控制寄存器,连续传输数据。

Blackfin DSP处理器支持二维DMA传输,特别适合于视频数据传输。二维DMA的相关控制寄存器如下:

配置寄存器(DMAx_CONFIG/MDMA_yy_CONFIG):设置二维DMA使能方式,中断产生方式。

内部循环计数寄存器(DMAx_X_COUNT/MDMA_yy_X_COUNT):保存二维DMA内层循环的数目(应≥2)。

内层循环地址增量寄存器(DMAx_X_MODIFY/MDMA_yy_X_MODIFY):保存每一次内层循环计数器加1后DMA操作地址在内存中的增量,此增量应该是二维DMA操作的数据单元长度的整数倍。

外层循环计数寄存器(DMAx_Y_COUNT/MDMA_yy_Y_COUNT):保存外层循环的数目。

外层循环地址增量寄存器(DMAx_Y_MODIFY/MDMA_yy_Y_MODIFY):保存每一次外层循环计数器加1后DMA操作地址在内存中的增量,可以是负值,此增量应该是二维DMA操作的数据单元长度的整数倍。

AT070TN83 V.1是群创生产的一款数字液晶显示屏,屏幕尺寸为7英寸(17.78 cm),分辨率800×480,23行消隐行。采用5 V(背光)和3.3 V(I/0)双电源供电。该液晶具有DE模式和HV模式,考虑Blackfin PPI的接口特点,本系统采用HV模式进行数据传输。

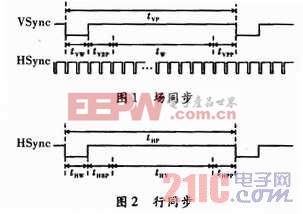

液晶时序如图1和图2所示。

图l和图2中相应的参数参照AT070TN83 V.1手册。液晶同步时序可以看做是满足一定要求的PWM波,可利用Blackfin DSP的定时器支持PWM输出的特性输出此信号。

2 系统总体设计

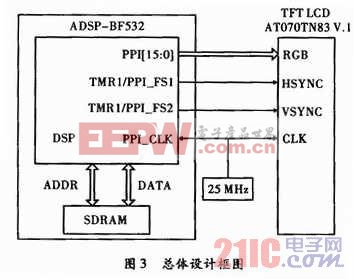

该液晶屏的输入格式为RGB666格式,而ADSPBF532的PPI接口数据线只有16位,根据人眼的视觉特性(对绿色最敏感),将红色和蓝色的最高位和最低位分别接在一起,其他数据线对应连接。

液晶所需的同步信号HS和VS分别由ADSPBF532的定时器1和定时器2产生。通过配置ADSPBF532定时器的相关寄存器可以精确地控制输出PWM

波的有效沿,周期和占空比,完全匹配液晶时序。

显示所用的时钟信号可以由外部的独立晶振产生,分别输入液晶和DSP的PPI口。也可以由DSP的输出时钟分频产生,再分别输入液晶和DSP的PPI口。本系统使用独立的25 MHz晶振将时钟信号直接输给液晶和PPI。

该液晶内部没有显存,因此在使用时系统需要扩展SDRAM,在SDRAM中开辟一块区域作为显示缓存,将需要显示的数据写入缓存,再由DMA传送到PPI口进行显示。

系统总体设计框图如图3所示。

在外部25MHz时钟的驱动下DSP按照寄存器的配置输出相应的同步信号,同时将SDRAM对应区域中的数据从PPI口输出。

3 软件设计

(1)显示缓存数据的存储。

该液晶每行800点,每个点对应16位数据,因此每行需要800×2 bit。每屏需要525行,包括前消隐23行,中间480行有效数据,后消隐22行,因此开辟显示缓存大小为525×800×2 bit。为了操作方便,可定义一个二维数组,二维数组中的数据与TFTLCD上的点具有对应关系(数组中每两个字节对应LCD上的一个点)。由于需要将显示缓存定义在SDRAM中,因此在工程中需要添加ldf文件,将

- 日立公司采用ADI的高性能Blackfin处理复杂算法及繁重I/O负载(01-16)

- Blackfin助您无线IP视频监控的应用(06-24)

- 基于Blackfin DSP的液晶接口设计(01-04)

- 基于ADSP-BF561的H.264视频编码器的实现(01-10)

- 基于ADSP-BF561处理器的视频编码器平台(01-16)

- ADI Blackfin?处理器架构概述 (07-12)