AT91RM9200微处理器的最小系统设计

引言

目前,ARM微处理器已在多种领域中应用,例如工业数字/智能控制、机器人、消费/教育类多媒体、DSP和移动式/便携式设备等。有关统计表明,各种各样 基于ARM微处理器的设备应用数量已经远远超过了通用计算机。因此,基于arm微处理器的开发应用正成为数字时代的应用技术潮流。本文介绍 AT91RM9200型微处理器最小系统的设计,并给出了系统外围接口设计的相关器件选型。

1 AT91RM9200简介

AT91RM9200是Atmel公司基于arm920T核的高性能、低功耗16/32位RISC(精简指令集计算机)微处理器,内部集成丰富的外设资 源,适用于要求外设资源丰富、功耗低、工作严格稳定的工业控制等方面,如嵌入式工业控制、医疗设备、网络通信、移动计算等。

AT91RM9200微处理器最高主频为180 MHz,其双向、32位外部数据总线支持8位、16位、32位数据宽度,26位地址总线可以对最大64 MB空间寻址。

AT91RM9200片内集成了非常丰富的外围功能模块,包括全功能MMU虚拟内存管理单元、内部16 kBSRAM和128 kB ROM、EBI接口控制器、增强的时钟和PMC(电源管理控制器),带有2个PLL(锁相坏)的片内振荡器,4个可编程的外部时钟信号,包括定时中断、看 门狗、秒计数器的系统定时器,带报警中断的实时时钟,带有8级优先级、可单个屏蔽中断源的AIC(先进中断控制器),7个外部中断源和1个快速中断源,4 个32位的IO控制器,20通道外围数据控制器(PDC或DMA),1个10 Mbit·s-1/100 Mbit·s-1以太网控制器,1个USB 2.0主机接口,1个USB 2.0设备接口,2个多媒体卡接口,3个SSC(同步串行口控制器)(兼容IIS),4个UASRT(通用同步/异步串行口),1个主/从SPI(串行设 备接口),1个两线串行接口TWI(主模式),JTAG/ICE接口等。

2 硬件设计

最小系统是保证微处理器可靠工作所必须的基本电路。基于AT91RM9200微处理器的最小嵌入式系统由微处理器AT91RM9200、电源电路、晶体振荡器电路、复位电路、JTAG接口、存储器模块、串行调试接口等电路组成,其原理框图如图1所示。

2.1 电源电路

在系统中,AT91RM9200需要1.8 V和3.3 V电源,另外,大部分外围器件需要3.3 V电源,小部分外围器件还需要5 V电源,为了简化系统电源电路的设计,假设系统的输入电压为5 V直流稳压电源。为了得到可靠的3.3 V电压,此处选用了Sipex公司生产的SPX1117M3-3.3型低压差(LDO)稳压器,它的输人电压为5 V,输出电流为3.3 V,最大输出电流为0.8 A。同样,选用Sipex公司生产的SPX1117M3-1.8型低压差(LDO)稳压器,便可产生最大输出电流为0.8A的1.8 V电源。电源电路如图2所示。

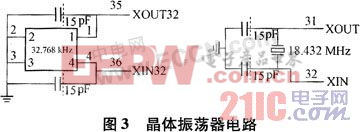

2.2 晶体振荡器电路

晶体振荡电路用于向AT91RM9200和其他需要时钟的外设电路提供工作时钟。本系统使用无源晶体振荡器X1(18.432 MHz)和X2(32.768 kHz)作为系统的主振荡器和慢时钟振荡器,振荡器产生的系统主时钟和慢时钟基准经过微处理器内部2个PLL后,产生系统所需的各种CPU时钟、外没时钟 以及USB器件工作时钟。晶体振荡器电路见图3。

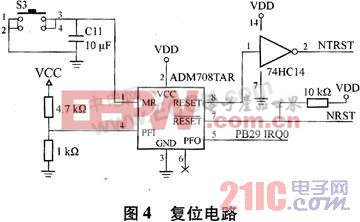

2.3 复位电路

AT91RM9200 有2个独立的复位信号,即系统复位信号NRST与系统内部调试复位信号NTRSI,都是低电平有效。系统上电后,AT91RM9200必须执行一个上电复 位(称为“冷”复位),在过渡状态下,它强制复位信号NRST和NTRST为低直到电源电压和振荡器工作频率稳定为止。此外,NRST和NTRST还可以 进行手动按键复位功能,以方便用户调试程序。本设计中选用了AD公司生产的ADM708型复位电路,它有一个手动复位输入引脚,当工作电压低于3.08 V或手动复位输入引脚被拉低时复位IC产生一个低电平信号,持续时间为200 ms。此外,该复位电路还有一个额外的输入电压检测引脚,可实现对输人电压的检测。复位电路如图4所示。

2.4 JTAG接口电路

JTAG(联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,是开发、调试嵌入式系统的一种简洁高效的手段。它有2种接门标准:14针接口和20针接口。本设计中选择20针接口标准。

2.5存储器模块

存储器模块包括Flash存储器和SRAM存储器两个部分。

Flash 存储器用于存储系统运行所需的程序和重要数据,即使掉电程序和数据都不会丢失。设计中推荐电路为Intel公司生产的28F640J3A,其存储容量为 64 Mbit(8 MB),工作电压为2.7 V~3.6 V,采用48引脚TSOP封装,16位数据宽度。它所需引脚为A[24:]、D[15:0]、NRST、BFCS_NCS0、CFOE_NOE_NRD、 CFWE_NWE_NWR0。

SDRAM存储器的作用是存放系统运行时的程序和数据,掉电后该部分程序和数据会丢失。设计中使用2片

ARM 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)