面向ASIC和FPGA设计的多点综合技术

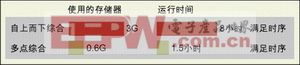

“自上而下”的综合方法考虑整个系统级RTL和约束,允许综合工具在一次操作中优化设计,而不必跨越分割的模块。与“自下而上”的设计相比,这种方法可产生最佳的QoR,因为综合工具是在整个设计上进行操作。由于不需要人工脚本和管理各种不同的子模块,它更易于实现。然而,它需要的存储容量和运行时间使之无法应用于大型设计中。即使很小的设计改动也要求重新对整个设计进行综合,这几乎是不切实际的。类似地,“自上而下”法要对复制的模块单独进行综合,与“自下而上”法对复制模块一次综合相比,这将导致更长的运行时间。最后,为了满足时序要求,布局与布线过程将变得非常反复。从QoR方面来看,“自上而下”法是理想的解决方案,但从设计规模或其它设计要求来看,它并不是每种设计的最佳选择。

多点综合:面向大型设计的综合技术

无论是单纯的“自上而下”法还是单纯的“自下而上”法都不是很多设计的正确解决之道。它们所需要的是集“自上而下”法的易用性及QoR优势与“自下而上”法的高效率及低存储器需求于一体的方法,而且这种方法仍要能够被自上而下或自下而上地使用。这一点在大型设计中尤其重要,因为现有的“自上而下”或“自下而上”流程不能获得最佳的QoR和运行时间。为了解决这个问题以及百万门ASIC和可编程系统级芯片(PSoC)设计者所面临的其它挑战,Synplicity公司开发了多点(MultiPoint)综合技术。

多点综合技术针对大型设计而采用了一种分层方法。与传统的“自下而上”分层设计不同,多点综合技术能自动分割和优化设计。这是对整个设计执行语言编译的结果,语言编译能创建一种中间格式,它包含所有分层信息以及设计的关键信息。Synplicity公司的ASIC解决方案使用内置的HDL分析工具,允许用户查看RTL设计分层或使用Tcl脚本来检查设计分层。通过审视逻辑分层,设计者将选择应该与其余设计部分分开综合的分层单元。在分层结构中,这些点被称为编译点。

一旦选定编译点后,时序约束将被施加到每一个点上;这个步骤最初将由人工执行,但未来可以自动完成。紧随其后,将从编译点开始对最低级别的设计层进行综合。随着每个编译点被综合,它会自动创建一个接口逻辑模型(ILM),并将其传递给下一个更高级别的设计层。最后,顶层是采用来自较低层编译的ILM以及顶层的任何额外逻辑来实现综合的。这能减少所需的时间,避免易出错的脚本,从而使设计团队可以将精力集中在设计的增值方面。

ILM是多点综合所采用的一项关键技术。ILM是Synplicity或第三方公司为网表或综合设计所编写的部分网表。它们是包含所有边界信息或时序分析逻辑的模型,因此能提供可与“自上而下”流程相媲美的QoR。由于ILM只包含从端口到寄存器的逻辑,而所有其它逻辑都被当成一个“黑箱子”来处理,因此它们大大降低了对存储器的需求,并减少了大型设计综合的运行时间。

用户自定义的编译点是创建ILM的基础,而且是多点综合技术的另一个关键要素。编译点是能够被独立综合的模块,然后综合的结果被用来综合其上级模块或顶层设计。多点综合与其它综合技术的一个关键区别在于,它能够通过三类不同的编译点(即软、硬和锁定编译点)来控制边界优化的层次。软编译点用于完全的边界优化,这意味着端口标识可以在综合期间改变。相反,端口完整性是由硬编译点保持的。对于锁定编译点,模块内的逻辑在优化期间能保持不变。因此,用户自定义的编译点可以充当综合工具的指令,以便对设计的某一特定部分进行建模和综合。由于允许跨边界的优化,这些编译点使 “自上而下” 的流程可以提供极佳的QoR。

多点综合技术正是通过用户自定义的编译点和ILM来支持IP集成。它能自动对IP建模,并利用综合的时序信息。在设计中充当范例的IP既可以在IP模块内又可以在相邻模块中进行逻辑优化,同时不会影响内核自身的端口安排。

对于同一IP模块的多个范例,多点综合技术可以确定每个独特范例的边界优化条件,而不必对各个范例进行再综合。多点技术采用一种独特的、基于差别的增量综合方法(见图1),它只对确实改变了的编译点模块进行再综合。只有那些因RTL、属性或约束条件发生变化而受影响的编译点才会被重新综合。通过比较新、旧RTL,多点综合技术可以智能地确定哪些变化是实质性的,因而有必要执行再综合。例如,RTL时间标记的改变、为RTL增加注释以及约束条件的重新排序

- 基于DSP的变电站综合自动化系统设计(01-27)

- 硬件描述语言Verilog HDL设计进阶之: 逻辑综合的原则以及可综合的代码设计风格(06-05)

- 基于FPGA的线阵CCD器件驱动器及其系统控制逻辑时序的设计(06-05)

- 一种基于Logical Effort理论的IC设计方法解析(06-05)

- FPGA设计者需要练好5项基本功(06-05)

- 基于HyperLynx的数字电路设计综合仿真方法(06-05)