嵌入式非易失性存储器在SoC物理设计中的应用

摘要:嵌入式非易失性存储器以其同时具备数据可更改性及掉电保存性而已被越来越广泛的应用于SoC物理设计。文中结合一款电力网控制芯片R36的实际设计案例,分析了该器件的应用特点,并从用途、性能、容量选择等方面说明了通过非易失性存储器对降低芯片成本、提高速度及可靠性应用方法。

关键词:非易失性存储器;电可擦除只读存储器;闪存;片上系统

0 引言

非易失性存储器是指在系统关闭或无电源供应时仍能保持数据信息的存储器,常见的有EPROM、EEPROM、Flash-EEPROM等。由于其同时具备数据更改性及数据保存性,NVM在系统设计中被大量应用于数据及程序的存储,并逐步替代部分有断电保存需要的RAM,甚至取代部分硬盘功能,如固态硬盘(SSD)。传统的系统解决方案采用外挂片外NVM芯片,这种方法会使系统复杂度提高。而随着嵌入式NVM技术的发展,将NVM与系统其它电路集成在同一块芯片中,已成为SoC系统设计的新趋势。相对于传统的片外NVM方案,嵌入式NVM具有更高的数据交换速度和更高的可靠性。然而,在SoC芯片的物理设计中,嵌入式NVM也面临工艺兼容、功耗及成本控制等新的问题。为此,本文以一款电力网控制芯片R36的物理设计为例,讨论了嵌入式NVM在实际应用中需要注意的问题,并给出了解决方案。

1 嵌入式NVM简介

1.1 嵌入式NVM的工作原理

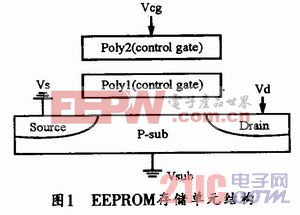

大部分NVM的工作原理都是以基本的EEPROM为存储单元。与普通MOS管相比,EEPROM存储单元多了一层多晶硅浮栅,图1所示是EEPROM的存储单元结构,该存储单元的基本操作为擦1、写0及读取。擦1时,Vcg为12 V,Vd为6 V,漏栅之间的电场使漏端电子穿越氧化层势垒而到达浮栅并存储,该过程称为热电子注入,这样,即使Vcg高压除去后,浮栅上的电荷也能保存很长时间;写0时,Vcg为-12 V,Vd为6 V,漏栅之间的电场给浮栅上的电子提供释放到P-sub的通路,称为FN隧道效应,此后,浮栅电荷被释放。

嵌入式NVM首先要解决的问题就是与芯片其它电路工艺(logic)的兼容。依据芯片中NVM所占面积的比重,嵌入式NVM通常有两种兼容方案。一是当NVM比重大于其它逻辑时,把logic工艺映射成NVM工艺,这是最方便的做法;二是当NVM容量较小(32 Mbits)时,为了节约产品开发时间,通常把NVM做成可复用的IP,然后映射成logic工艺。

1.2 常见的嵌入式NVM

目前常见的嵌入式NVM有EEPROM和flashEEPROM(简称flash)两大类,EEPROM每个存储单元都配有一个门控开关,故可实现单元独立擦操作;而flash存储单元没有独立的门控开关,通常以page为单位进行擦操作,因此,相同容量的EEPROM面积会大于flash,但单个单元擦写时间则小于flash,且擦写时不影响其他单元的状态,同时,使用寿命较flash有很大的优势。常见的flash也因其架构不同,可分为NORflash和NANDflash两类,NAND flash架构更为紧凑,成本/容量比更优,但目前嵌入式技术相对没有NOR成熟。

1.3 嵌入式NVM的选择

选择嵌入式NVM是一个综合衡量成本、功耗及性能的过程。因为嵌入式NVM通常会增加工艺步骤,使芯片制造的一次性成本和持续性成本都增加,同时,NVM的测试时间远大于芯片中的普通SRAM和ROM,因而增加了芯片的测试费用。因此,在选择NVM时,要从系统角度考虑以下几方面因素:

(1) NVM的用途。程序存储通常选用EEPROM或NOR flash,数据存储通常选用NANDflash;

(2) NVM容量。容量和面积、成本息息相关,小容量的NVM可以采用单位面积大但工艺更简单的特殊单层多晶工艺,而大容量的NVM则应采用面积紧凑的通用双层多晶工艺;

(3) NVM性能。通常需要考虑NVM的擦写时间、工作温度等参数;

(4)NVM的可靠性。可靠性主要有两个指标,即数据保存时间和数据擦写次数,若要较高的擦写次数,则EEPROM要优于flash。

2 嵌入式EEPROM

2.1 R36电力网远程抄表芯片简介

R36电力网远程抄表芯片是集成了模拟接口、m8051处理器、SRAM、ROM及EEPROM的SoC,其前身为外挂片外flash芯片的R35芯片,R36采用多晶片封装(Multi Chip Package,MCP),这种封装方案增加了芯片的制造成本,同时增加了系统的复杂程度,而且也降低系统的可靠性。而采用嵌入式EEPROM设计的R36将所有器件集成在一片芯片中,则使用普通封装即可,因而避免了上述问题。

R36采用SMIC 0.18μm EEPROM工艺,主要用来存储程序,故可依据需要选择SMIC 32KB及1KB的EEPROM IP各一个。该芯片已于2010年3月成功流片。

2.2 工艺映射

与普通logic工艺相比,SMIC EEPROM工艺需要多加9层掩膜和10次光刻,主要增加POLYl和ONO层,且其POLY2层与logic的POLY层在同一平面上,因此,在物理版图设计过程中,需要将EEPROM的POLY2层映射为POLY层,设计时可用通用的logic流程进行布局布线,并在生成最终GDSⅡ时,再将POLY层映射回POLY2,这样即可按EEPROM工艺流片。

2.3 布局布线

在芯片的布局阶段,需要仔细考虑EEPROM芯片的摆放位置。除了遵循一般嵌入式存储器摆放规则(尽量远离模拟模块)外,还需注意将EEPROM与其他电路之间留出足够隔离的空间(>5um),以防止噪声干扰;同时,所有EEPROM的摆放方向必须一致。在布线阶段,要给EEPROM提供充足的工作电源及稳定的参考电压,并禁止在EEPROM上层绕线以防噪声。图2所示是最终的芯片版图。

设计 应用 物理 SoC 易失性 存储器 嵌入式 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)