FAE讲堂:利用赛灵思FGPA实现降采样FIR滤波器

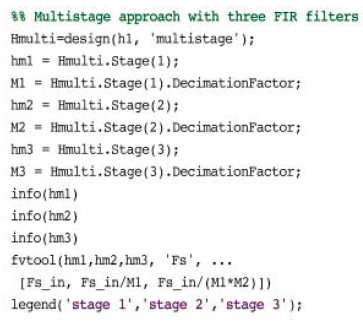

指令信息,您可以看出:它会提出三级解决方案建议,其抽取因数分别是M1=2、M2=5和M3=5。

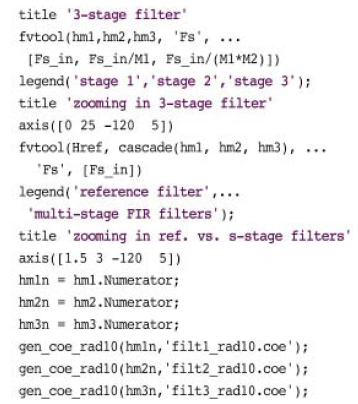

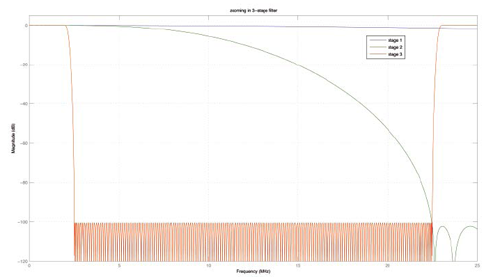

图3显示了组成上述多级系统的三个滤波器的频率响应。蓝色曲线代表第一个降采样滤波器(M1=2);绿色曲线代表第二个滤波器 (M2=5),按Fs_in/M1倍数周期波动;而红色曲线则代表第三个降采样器 (M3=5),按Fs_in/(M1*M2)倍数周期波动。

图 3. 通过串联三个FIR滤波级进行的按 50 整数抽取,此处单独放大显示0~25MHz频率。

用于三级滤波器的FIR-Compiler设置与图1及图2所示大同小异。第一个滤波器唯一不同的参数是COE文件名和“抽取率值”,其分别设为filt1_rad10.coe和M1=2。第二个滤波器COE文件名是filt2_rad10.coe,抽取率值为M2=5,输入采样频率此时为125MHz,因为第二级按M1=2抽取来自第一级的输入数据。最后,第三个滤波器参数的唯一区别是COE文件名为filt3_rad10.coe,抽取率值为M3=5,输入采样频率此时为25MHz,因为第三级按M2=5抽取来自第二级的输入数据。

在布局布线后,三个滤波级占用以下FPGA资源:

第一级(M1=2):

Slice触发器数量:280 个

Slice LUT数量:208 个

占用 Slice数量:62 个

DSP48 MAC单元数量:3个

第二级(M2=5):

Slice触发器数量:236个

Slice LUT数量:168 个

占用 Slice数量:60 个

DSP48 MAC单元数量:3 个

第三级(M3=5):

Slice触发器数量:357 个

Slice LUT数量:414 个

占用 Slice数量:158 个

DSP48 MAC单元数量:4 个

由于采用上述多级方法,我们现在比参考滤波器最初的22个DSP48 MAC单元少用了12个单元;与单级理想滤波器占用资源相比,我们节约了30%左右的触发器,55%的LUT,44%的slice和54%的DSP48单元。

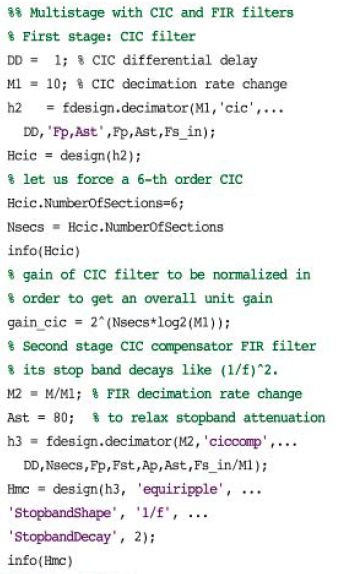

与CIC滤波器串联

另一种按50抽取的可行方法是把级联积分梳状 (CIC) 滤波器 和CIC补偿降采样级串联在一起,其变化速率分别为M1=10与M2=5。CIC滤波器是一类特殊的FIR滤波器,由N个梳状滤波器和积分器组成(因此产生“第 N 级”术语)。尽管梳状滤波器仍然可以实现成一种“传统的”基于MAC的FIR滤波器,不过CIC架构之所以有趣是因为它不需要任何MAC单元,因此可以用CLB sclice替代DSP48单元,参阅CoreGen CIC-Compiler 1.3数据手册(cic_compiler_ds613.pdf)。

按M1=10抽取的第一级CIC滤波器频率响应较差,因此需要采用一个按M2=5抽取的补偿FIR滤波器,以弥补第一级CIC滤波器本身通带的下降。以下MATLAB代码说明如何采用FDA工具设计此类滤波器。

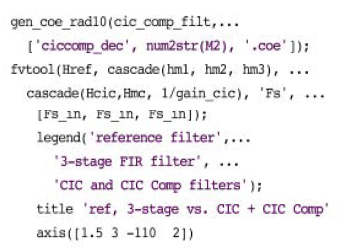

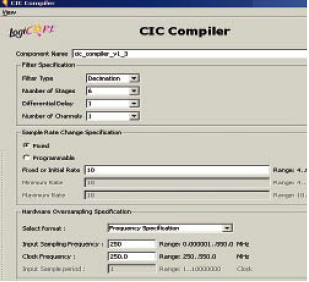

图4为赛灵思CoreGen CICCompiler 1.3 GUI设置的第一个页面;其它参数采用默认值,“使用Xtreme DSP Slice”可选参数除外(GUI 的第2页(共3页)),

图 4. 按10抽取的CIC滤波器的设置。CIC-Compiler 1.3 GUI的第1页(共 3 页)。

其允许采用或不采用DSP48单元实现梳状滤波器。FIR Compiler GUI中的CIC补偿FIR滤波器设计参数与图1及图2所示相同;唯一不同的设置是 COE 文件名(此处是ciccomp_ dec5.coe),抽取率值为M2=5,而输入采样频率为25MHz。

在布局布线后,两个滤波级占用以下FPGA资源:

第一级(按10抽取的CIC滤波器,不使用“采用Xtreme DSP Slice”)

Slice 触发器数量:755 个

Slice LUT 数量:592 个

占用 Slice 数量:172 个

DSP48 MAX 单元数量:0 个

第一级(按10抽取的CIC 波器,使用“采用 Xtreme DSP Slice”)

Slice 触发器数量:248 个

Slice LUT 数量:154 个

占用 Slice 数量:42 个

DSP48 MAC 单元数量:7 个

第二级(按5抽取的CIC补偿FIR滤波器)

Slice 触发器数量:271 个

Slice LUT 数量:312 个

占用 Slice 数量:114 个

DSP48 MAC 单元数量:3 个

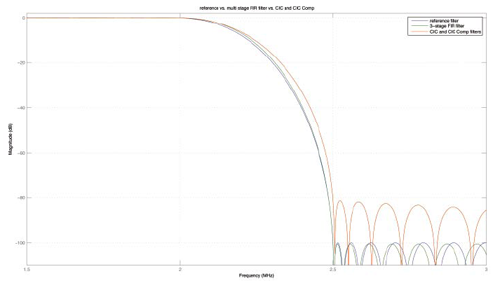

两种结果都很有趣,而是否选择使用Xtreme DSP slice取决于设计人员最需要节约哪些资源。我个人选择“采用Xtreme DSP Slice”选项。与单级滤波器相比,我们可以节约大约59%的触发器,73%的LUT,69%的slice和54%的DSP48 MAC单元。代价是阻带衰减更差,其现在是80dB,而非所需要的100dB,如图5所示。某项设计是否接受该衰减值事实上与应用相关。

图 5. 三个降采样器的频率响应 - 整体速率变化为50,图中显示了放大的1.5~3MHz频段。单级滤波器为蓝色,三级滤波器(比例分别为M1=2、M2=5、M3=5)为绿色,基于CIC的二级滤波器(比例分别为M1=10、M2=5)为红色。

图5对比上述三种按50降采样方法:单级、三级(比例为 2-5-5)和CIC滤波器与CIC补偿FIR滤波器串联(比例为10-5)。

有理数降采样

在此第二个应用示例中,我们假设信号输入数据速率是50MHz,其必须降采样到12

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序(07-15)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 利用NI CompactRIO与NI Single-Board RIO实现从快速构造原型到低成本发布(03-19)

- 创建还是购买:什么是您嵌入式设计的最好选择?(07-06)

- Pmod规范,或Arduino伪标准(08-27)