英特尔试制48内核处理器,备战多核时代

美国英特尔开发出了将48个CPU内核集成在1个芯片上的研究用处理器"Single-chip Cloud Computer(SCC)"。新产品投产的计划没有公布,据悉目前仅将试制的芯片提供给大学等研究机构,以供在多内核芯片上运行软件及编程模型(Programming Model)的研究。

英特尔设想的远景是,通过这种多内核芯片,"可使配备3维摄像头的笔记本电脑获得与人类视觉同样的高精度识别物体及动作的能力,或者在网上购物时起到镜子的作用,供消费者虚拟试穿自己喜欢的衣服"(英特尔公司)。

双核是48内核微处理器的构成单位

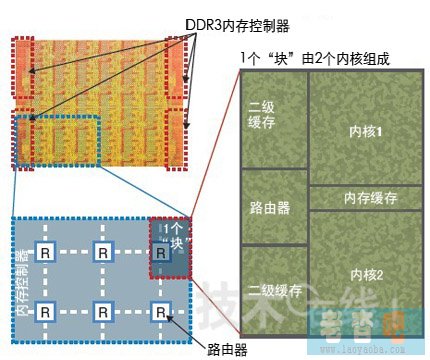

SCC是在1个芯片上排列6×8个CPU内核后构成的微处理器。不过,其实质是"重现了将双核芯片以网络方式相互连接的构造"(英特尔)。这也是"云计算(Cloud Computing)"这一名称的由来。具体而言,芯片被划分为24枚名为"块"的小单位(图1)。而且,这种"块"结构,其每一枚都与分别具备二级缓存的2个CPU内核等所构成的老式双核微处理器相同。

图1 将24组双核处理器通过"路由器"相互连接

图为英特尔的48内核微处理器的结构。48内核的结构是,由24个2个内核1组的"块"通过网格状网络连接而成。芯片的制造工艺采用了45nm工艺技术以及high- k金属栅极。(点击放大)

"块"中集成了名为"路由器(Router)"的开关电路。路由器之间以二维网状相连接,并可与其他"块"交换数据。数据传输的带宽方面,"在对分(Bisection)条件下为256GB/秒"(英特尔公司)。所谓对分,是指通过被切为两半的该芯片断面的数据传输带宽的合计。其数值与高性能超级计算机相当或者要高。

英特尔2006年曾发布了80内核的试制芯片。80内核芯片的各内核仅能进行浮点计算,而此次各内核可运行86指令集。

而作为80内核芯片特点之一的、将内存直接贴合在各内核上进行堆叠的技术,"目前研究所正在进行开发,不会应用到此次芯片上"(英特尔公司)。

内核之间实现有机联动

此次芯片并不是仅单纯增加了内核的数量,还可根据应用的不同,在内核间进行联动处理。例如,当任务之间相互关联时,则可由相邻的内核来执行这些任务,像组装流水线那样,将运算结果从某个内核直接移动到相邻的内核。这样向外设内存中存取数据的频度就能降低。

另外,面向数据交换用途,此次处理器还配备了以各内核共享1个内存方式运行的"shared virtual memory(SVM)"功能。其方法是通过虚拟技术,在物理上将其他内存当作共享内存来使用。英特尔表示,这样电路构成就变得更单一,内核间数据传输的延迟也变得更小。

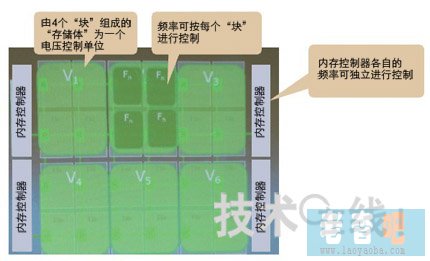

该芯片的另一大特点是耗电量仅为25~125W(图2)。这是通过对工作频率及工作电压进行细微控制从而实现的。工作频率以"块"为单位、工作电压以由4枚"块"组成的"存储体(Bank)"为单位独立进行控制。芯片外围集成了4个内存控制器(Memory Controller),而且其工作频率及工作电压可有别于其他内存控制器,独立进行控制。这样,工作频率便可在28个区段、工作电压可在8个区段独立进行控制。

图2 工作频率分28个区段、电压分8个区段进行控制

为了降低耗电量,工作频率按每个"块"进行控制。内存控制器的频率也可独立进行控制。而电压则以名为"存储体"的4枚"块"为1组的单位进行控制。(点击放大)

16内核产品受挫使得此次产品备受瞩目

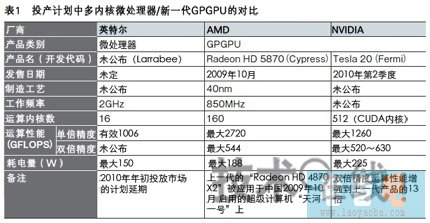

在发布了该48内核处理器之后,英特尔推迟了该公司原计划2010年年初推出的16内核微处理器"Larrabee"的供货。有业内人士认为,事实上这是无限延期。

已公布的信息显示,Larrabee与此次的48内核处理器同样配备SVM功能,另外,其在2009年11月超级计算机技术国际学会"SC09"上的单倍精度下浮点运算性能达到了约1TFLOPS。开发屡次延期,使其相对于竞争对手的美国AMD(Advanced Micro Devices)以及美国NVIDIA的图形处理LSI(GPU)产品的优势丧失殆尽,这被认为是此次延期上市的原因(表1)。

CPU内核多核化的发展方向,已成为包括竞争对手在内也在致力研发的一大趋势。英特尔投产的多内核微处理器,有可能一举跃升到48内核。

- 英特尔联手阿朗推出WiMAX互操作性测试计划(02-17)

- 华为与英特尔成立互操作实验室 共促TD-LTE产业(05-02)

- IDT与英特尔合作开发共振技术无线充电IC(09-04)

- 英特尔加入无线充电联盟A4WP(07-03)

- 英特尔收购富士通旗下无线射频芯片子公司(08-15)

- 加速4G/LTE芯片上市进程 英特尔成立无线认证实验室(09-09)