基于DSP和高速A/D的电力系统多通道同步采样

摘要:介绍了一种以DSP芯片TMS320C6711D为处理核心,辅以高速A/D芯片ADS8364,实现电力系统多通道同步采样分析的系统结构,着重介绍系统的硬件设计,通过测试及使用表明,该设计使用方便、实时性好、抗干扰性强、测量精度高、性价比优,可在电力系统中广泛使用。

关键词:DSP;交流同步采样;电能质量

基本电量的采集作为电力系统实时控制、监测、调度自动化的前提环节,毫无疑问具有重要的作用。如何准确快速地采集电力系统中的各个模拟量并加以分析,以达到实时报警甚至预防事故发生的目的,是电力系统研究中的热点。

文章描述的采样分析系统选用美国TI公司的TMS320C6711D作为主要的计算核心器件,该芯片具有900 MHz FLOPS高速浮点运算能力和类似RISC的指令集,采用VeloeiTI先进VLIW结构内核:8个独立的功能单元,6个ALU,2个乘法器,浮点支持IEEE标准单精度和双精度浮点运算,可以每周期执行8条32 bit指令,带有32个32 bit通用寄存器。

A/D转换电路的核心是芯片ADS8364,ADS8364是一种高速、低功耗、6通道同步采样转换器件,它是16位高速并行接口的模数转换芯片。每片ADS8364由3个转换速率为250 ks·s-1的ADC构成,每个ADC有2个模拟输人通道,每个通道都带有采样保持器,3个ADC可组成3对模拟输入,可对其中的输入信号同时采样保持。另外,引脚内部还带有2.5 V电压接口,可用以提供基准电压。由于6个通道可以同时采样,因而适用于需同时采集多种信号的应用场合。

当ADS8364采用5 MHz的外部时钟来控制转换时,它的取样率是250 kHz,同时对应4μs的最大吞吐率,即采样和转换共需花费20个时钟周期。因此,为了得到最大的输出数据率,读取数据可以在下一个转换期间进行。

1 基于DSP和高速A/D的系统设计

整个系统可分为三相同步锁相电路、A/D转换电路、DSP核心部分电路以及HPI总线连接等4大部分组成。实现数据采集以及各种核心算法,并可以通过高速数据总线(HPI)将计算所得的数据实时传递。原理图如图1所示。

1.1 三相同步锁相电路

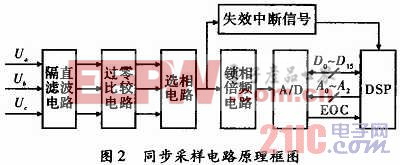

同步电路主要完成频率跟踪的功能,该电路可以保证在一个工频周期内为A/D提供256点的采样信号,从而实现同步锁相的功能。

如图2所示,通过电压互感器得到的电压信号经过隔直滤波电路,然后进入过零比较器,得到一个与输入信号同频率的TTL电平的方波信号后,再经过整形电路,得到一个上升沿陡峭、波形规则并且频率与输入电压信号相同的CMOS电平方波,进入选相电路。

选相电路能自动选择有电压的相别,并根据选中相别的电压产生过零信号提供给后续的PLL电路,以实现256倍的锁相倍频采样。在频率变化的情况下,电路也能保证每周波256点的采样。选相电路以A相电压作为最优先考虑的相别,当A相有电压时将A相过零信号作为同步信号,闭锁B、C相;A相掉电后,以B相过零信号作为同步信号,闭锁C相;A、B相同时掉电,以C相过零信号作为同步信号。在相间进行同步信号切换时,由于电路参数以及线路本身的延时,会出现一段闭锁的空白,这时将产生一个中断信号通知DSP,由DSP提供这个空白时间的同步采样信号。当三相电压全部失去后,则由DSP自主产生同步采样信号,以50 Hz工频进行256点采样,如图2所示。

1.2 A/D模数转换电路

模拟变换、信号调理及A/D转换构成整个A/D模数转换电路,此电路是整个采样系统的基础,它实现了电压互感器、电流互感器二次侧的信号隔离、变换适合于A/D采样的模拟输入信号,如图2所示。A/D转换器则将经过调理的模拟信号转换成DSP能够识别的对应的二进制数字信息。

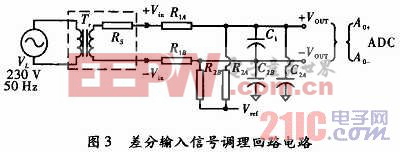

互感器信号采用差分输入方式,这种输入方式抗干扰能力很强。其连接的原理图如图3所示。当±Vin输入最大为-2.5~2.5 V的交流信号,Vref使用+2.5 V的基准时,使得调理输出±Vout范围在0~5 V,该电路参数可以正好满足所选A/D芯片ADS8364的输入要求。

A/D转换结束后产生一个中断信号EOC通知DSP读取数据,DSP通过地址选择相应A/D芯片及相关通道后,将16位数据读回。DSP以A/D转换器采集转换后的三相电压、三相电流实时数据作为计算基础。

1.3 DSP核心部分电路

DSP及其外围接口电路是整个系统的核心,它由32位浮点DSP、振荡器+锁相倍频器、电压监测及看门狗电路、片外SDRAM、片外Flash、片外铁电存储器等电路组成。如图4所示,电路实现了整个系统的上电复位、看门狗、电压检测以及扩展管理芯片对系统复位的功能。

外部的25 MHz振荡器通过倍频芯片和二进制计数器分别对DSP和AD转换器提供同步的150 MHz和3.125 MHz工作时钟。

DSP在上电复位以后,首先通过EDMA方式自动加载Flash前1 kB的Bootload程序,在该Bootload程序里写入后续加载程序的入口地址,即可实现应用程序的自动加载工作。之后对SDRAM进行自检,以避免SDRAM单元出错造成工作不正常或数据出错,同时SDRAM也是DSP存储A/D采样数据、进行数据运算输出的中间及最终结果、通信等数据缓存的场所。

FRAM可以实现在失电下保存数据,并且读写次数超过1012次,可以实现无延时写入。该FRAM通过DSP的McBSP接口相连,存储ADC每个模拟通道的DC偏移、精度修正的数据以及运行时的接线方式等参数。

DSP处理完成的数据,通过其内部集成的主机接口(HPI)与上位机进行数据交互,主机可以通过DMA或EDMA方式随机或整块地访问共享RAM7。

2 采样系统的软件设计

系统的软件设计基于TMS320C6711D芯片指令集,充分利用其高速,支持浮点运算,流水线操作等特点,采用C语言和汇编语言混合编程,遵循模块化、自顶向下、逐步细化的编程思想。程序使用模块化设计,主要包括采集模块、主循环模块和HPI交互协议模块3大模块,流程框图分别如图5~图7。

- 嵌入式同步时钟系统的设计与实现详解(05-19)

- 多通道同步数据采集及压缩系统(08-12)

- Mobileye获MIPS32 1004KTM同步处理系统授权(04-17)

- 基于DSP的高阶COSTAS锁相环的设计(03-02)

- 基于Android系统的影音播放器开发(03-25)

- Linux多线程同步方法(07-29)