I2C总线接口逻辑分析

1 前言

I2C总线是具备多CPU系统所需的包括仲裁和高低速设备同步等功能的高性能串行总线。它以两根连线实现完善的全双工数据传送,是各种总线中使用信号线根数最少,并具有自动寻址、多主机时钟同步和仲裁等功能的总线。

目前世界上采用的I2C总线有两种规范,它们分别是由荷兰飞利浦公司和日本索尼公司提出的。现在广泛采用的是飞利浦公司的I2C总线技术规范,它已成为被电子行业认可的总线标准。

由于I2C总线具有标准的规范及众多带I2C接口的外围器件,使得使用I2C总线设计计算机系统变得十分方便、灵活,体积也小,因此在各类实际应用中得到广泛使用。

2 I2C总线的基本原理

2.1 I2C总线基本结构

I2C总线系统结构灵活,易于模块化、标准化设计。I2C总线只有两根信号线,一根是数据线SDA,另一根是时钟线SCL。所有进入I2C总线系统中的器件都带有I2C总线接口,符合I2C总线电气规范的特性;而且采用纯软件寻址方法,无需器件片选线的连接。CPU不仅能通过指令将某个功能器件挂靠或摘离总线,还可对其工作状况进行检测,从而实现对硬件系统即简单又灵活的扩展与控制。各器件供电可不同,但需共地。另外,SDA、SCL需分别接上拉电阻。

SDA、SCL都是双向的,输出电路用于向总线上发送数据,输入电路用于接收总线上的数据。当总线空闲时,两根线都是高电平。连接总线的器件的输出端电路必须是集电极开路输出或开漏输出,以具有线“与”功能。I2C总线的数据传送速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下则可达3.4Mbit/s。

I2C总线接口电路结构如图1所示。

2.2 I2C总线数据传送

I2C总线数据传输时必须遵循规定的数据传送格式,如图2所示为一次完整的数据传送格式。启动信号表明一次传送的开始,其后为寻址字节,该寻址字节由高7位地址和最低1位方向位组成:方向位为“0”表明写操作,“1”表明读操作;在寻址字节后是由方向位指定读、写操作的数据字节与应答位;在数据传送完成后为停止信号。在“启动”与“停止”之间传送的数据字节数从理论上来说没有限制,但每个字节必须为8位,而且每个传送的字节后面必须跟一个应答位。

当SCL为高电平时,SDA由高电平跳变为低电平,定义为启动信号;当SCL为低电平时,SDA由低电平跳变为高电平,定义为停止信号。

在SCL为高电平时,SDA上数据需保持稳定方被认为有效;只有在SCL为低电平时,才允许SDA电平状态变化。

2.3时钟信号的同步

在I2C总线上传送信息时的时钟同步信号是由挂接在SCL线上的所有器件的逻辑“与”完成的。SCL线上由高电平到低电平的跳变将影响到这些器件,一旦某个器件的时钟信号下跳为低电平,将使SCL线一直保持低电平,使SCL线上的所有器件开始低电平期。此时,低电平周期短的器件的时钟由低至高的跳变并不能影响SCL线的状态,于是这些器件将进入高电平等待的状态。当所有器件的时钟信号都上跳为高电平时,低电平期结束,SCL线被释放返回高电平,即所有的器件都同时开始它们的高电平期。其后,第一个结束高电平期的器件又将SCL线拉成低电平。这样就在SCL线上产生一个同步时钟。可见,时钟低电平时间由时钟低电平期最长的器件确定,而时钟高电平时间由时钟高电平期最短的器件确定。

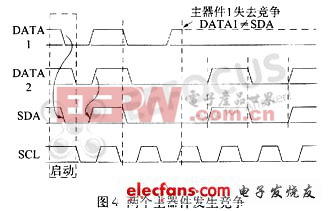

2.4 总线竞争的仲裁

总线上可能挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况,这种情况叫做总线竞争。I2C总线具有多主控能力,可以对发生在SDA线上的总线竞争进行仲裁,其仲裁原则是这样的:当多个主器件同时想占用总线时,如果某个主器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级。总线竞争的仲裁是在两个层次上进行的。首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性。由于是利用I2C总线上的信息进行仲裁,因此不会造成信息的丢失。

3 I2C总线接口逻辑的构成

3.1 I2C总线接口电路的结构

I2C总线接口逻辑框图如图5所示。

在电路设计中,各功能块的硬件实现介绍如下。

启动、停止检测电路应用两个D触发器来分别响应SDA在SCL为高电平时的电平跳变。

移位寄存器电路由9个D触发器串联成9级移位寄存器,包括8位字节和1位应答位,实现SDA上数据的串并行转换。寄存器复位值为“111111110”,接收8位字节后为“0D7D6D5D4D3D2D1D0”,即应答位为“0”,在第9个时钟时输出低电平作为应答信号。

可编程地址发生器电路生成器件地址,7位器件地址由器件编号地址(高4位)和引脚地址(低3位)组成。通过改变器件引脚的连接方式,就可改变器件地址,因此使应用方便灵活。

地址比较器电路由门电路组成布尔代数式逻辑,对寻址字节进行判断。若地址正确则将RS触发器置“1”,使能译码器输出。

3.2 I2C总线接口工作流程

I2C总线接口工作流程如图6所示。

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 关于Linux操作系统的NTFS和内核分析(05-19)

- Linux 2.4.x内核软中断机制(04-06)

- 基于DSP的人脸识别系统设计(04-26)

- 3D图形芯片的算法原理分析(07-16)

- 解析:视频图像智能分析处理技术(08-08)