基于USB 2.0协议的高速图像传输系统

用户自定义请求,通过控制PA0,PA1的高低电平,以控制整个硬件系统的运行。该系统中,使用0xB3使PA0置低进行图像数据的上行操作,用0xB4使PA0置高进行图像数据的下行操作,使用0xB5使PA1置低来通知硬件开始传输,使用0xB6请求使PA1置高以通知硬件系统停止传输。

USB设备驱动程序负责建立起主机端和设备端的联系。驱动程序主要有两个:一是开机自动将固件程序下载至芯片RAM中,以由增强性8051执行。结合CYPRESS开发包EZ-Loader Drivers以及HEX2C和Windows DDK即可生成所需要固件自动下载程序.sys文件。二是完成上位机应用程序和硬件设备之间的数据传输。其主要包括驱动程序入口例程、即插即用例程、分发例程、电源管理例程和卸载例程。本系统根据通用驱动结合自身需要,在DDK环境下修改编译,生成自己需要的驱动程序。USB上层应用程序都通过I/O控制来访问设备驱动程序。上层应用程序首先通过调用Win32函数CreaFile()来取得访问设备驱动程序的句柄;然后应用程序使用Win32函数Devi-ceIoControl()来提交I/O控制码,并且为CreatFile()函数返回的设备句柄设置I/O缓冲区。该系统中,设置USB端口缓冲区FIFO为1 024 B,端口非空即读取。保持了传输的连续性,并且每次以帧结构包形式传输,每包的大小为512 B。以实验中为例。每传输大小为245 KB的一幅图像,需要490个包进行传输。

接收端应用程序流程图如图3所示。发送端应用程序流程类似,少了判断图像是否完整一幅,而多了传输完毕之后的图像数据校验。

2 系统仿真及实现

图4所示为图像发送系统主要端口的ChipScope实测波形,所用FPGA为V4-XC4VSX55。

USB_Data为传输的图像数据。数据长度为16位,SLRD为异步读取FD总线的时钟,采用USB时钟源48 MHz四分频得到,FIFO指针在每次SLRD激活到撤消激活变化时累加,即每变化一次,读取FIFO里16 b缓存数据一次。SLOE引脚为读写使能信号,默认低电平有效。从该实测图可以看出,三路信号均符合异步读取的时序要求。

主机接收端应用程序采用Delphi语言编写,图像传输它采取传输的同时显示图像的形式。从上位机应用程序截取一幅接收图像如图5所示。该应用程序主要用于各种调制方式下图像的传输。可以看到传输图像清晰完整,连续显示没有滞后,没有噪声斑点。图像经过USB接口传输后没有数据丢失,比较清晰。实验证明,图像传输过程中,没有出现丢帧的情况。满足实时高速的图像传输。

3 结 语

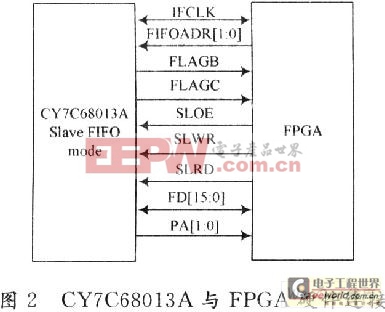

USB 2.0技术以其高速传输和使用方便受到广泛的关注,其应用也必将越来越广泛。上述设计方案有效地解决了图像传输过程中的高速通信问题。系统中采用异步方式传输,采用芯片所提供四分频时钟,最高速率可达到192 Mb/s。采用FPGA和USB 2.0相结合的方式,数据处理能力得到极大的提高,由于采用CY7C68013A的Slave FIFO模式,可使用外部FPGA并按照用户需求设计,增强使用功能的多样性和灵活性。该方案亦可应用于大容量、高速度的实时数据采集,音频及视频传输等领域。

- 利用FPGA实现外设通信接口之: 典型实例-USB 2.0接口的设计与实现(06-05)

- 利用FPGA实现外设通信接口之:利用FPGA实现USB 2.0通信接口(06-05)

- 基于总线的嵌入式高速图像通信系统设计(12-21)

- 基于USB 2.0数据采集系统的程序设计(12-21)

- USB2.0接口全接触(12-14)

- 如何轻松地将USB 2.0变为USB Type-C(12-13)