基于ARM和FPGA的声纳波形产生系统设计

选用Altera公司的Cyclone II系列的EP2C20F484C8N。

4、系统软件开发

本系统的软件主要分为主控设备应用程序设计,FPGA波形设计部分和ARM控制部分。

主控设备应用程序是在X86平台上,VC环境下开发的。主要功能是通过RS232串口,并口EPP或USB任何一种通讯接口,实现主控设备与ARM通信。ARM控制部分的程序实现对通讯接口的访问,并实现对FPGA的控制。

FGPA波形设计过程采用自顶向下模块化的结构,主要包括时钟模块、寄存器读写及控制模块、DDS模块,如图4所示。

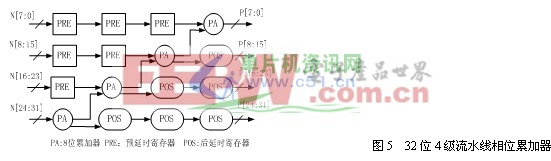

相位累加器是决定DDS性能的一个关键部分,相位累加器设计的好坏将直接影响到整个系统的性能,因此要从FPGA内部结构出发,设计出既节约系统资源,又能大幅度提高系统速度和性能的累加器结构[3]。在设计相位累加器的加法器模块时不用库中提供的lmp_add_sub模块,而是采用流水线技术,使用Verilog HDL编程实现。流水线示意图见图5。

相幅转换采用ROM查找表法实现。主要考虑的问题是FPGA内部存储器容量的大小,而EP2C20内部有大量的ROM资源可利用,因此可直接调用lpm_rom模块来实现。

FPGA模块化的设计,为ARM对其配置提供了极大的方便,ARM可把FPGA视为外挂的一片SRAM,通过外部存储器接口进行控制。

5、软硬件设计需要注意的几点

在系统软硬件设计中需要注意以下两点:

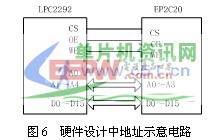

(1)当LPC2292通过外部存储器接口(EMC)控制FPGA时,地址线的接法如图6所示,即需要把LPC2292的地址线A0空出来不用。这是由于FPGA实现的波形产生模块的数据位宽为16位,当LPC2292外部存储器总线配置为16位时,A0地址需要空出来,当总线配置为32位时,地址A0,A1都需要空出来,当总线配置为8位时,地址从A0开始使用。

(2)EP2C20F484C8N的焊接问题,此型号为FinleLine BGA封装,在焊接的时候要注意芯片的锡球是否含铅,含铅与否决定采用何种工艺流程将器件安装在PCB板上,无铅封装要求焊接温度更高,工艺更复杂。Altera公司生产的所有无铅元件以其产品序号最后的“N”标出。因此本系统选用的芯片为无铅芯片,需要按无铅工艺焊接,若按有铅工艺焊接,将造成芯片的虚焊。

6、系统测试结果

对系统软硬件进行的测试表明,系统达到了预期的设计指标,能输出7路方波信号,频率固定(CW波)或线性变化(LFM波),且各路信号可选择关断或选通。CW波的频率在5~45kHz范围内任意可调;LFM波在5kHz带宽范围内任意可调,中心频率在5~45kHz范围内任意可调;输出脉冲信号宽度在0.5~100ms间任意可调,相邻各路信号的相位可超前和滞后,可选择发射功率,且本系统已成功应用于某工程项目中,工作正确可靠,得到了工程实际检验。图7为Tektronix逻辑分析仪采集到的对应输出的CW波。

7、结论

该系统很好的利用了ARM和FPGA两者的长处,ARM集中实现主控设备与FPGA通信的桥梁作用,接收主控设备发出的声纳波形参数,并根据这些参数配置FPGA内部的寄存器;FPGA充分体现了它在系统成本、体积上的优势,设计灵活、方便,FPGA的使用为系统的升级带来了很大方便。同时通讯接口的多样性,极大改善了人机接口,提高了系统的灵活性。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)