嵌入式 FIFO 数据传输系统设计

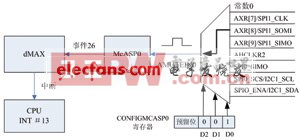

图3 中断功能设置框图

从图3中可以看出,配置好音频串口后,一旦AXR[8]引脚有上升沿到,则McASP0激活dMAX的事件26,向CPU发送内部中断13。McASP的与中断相关的寄存器配置是实现以上方案的重点。使用PFUNC寄存器将其配置成通用IO引脚;PDIR寄存器控制IO引脚的方向;如果是输出引脚则由POUT引脚输出高低电平,如果是输入引脚,则由PDIN寄存器读出该引脚的状态;此外,可以使用PDCLR和PSET寄存器清除或者设置输出引脚的状态。

系统软件设计

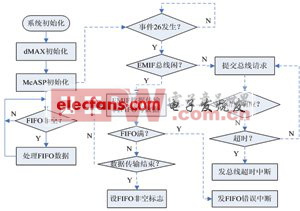

系统软件设计主要包括McASP的初始化、dMAX的初始化、FIFO的初始化、中断使能等。系统主程序只需要等待中断进行相应的处理,主要的数据传输工作都是dMAX按照软件配置自动完成,不需要CPU参与。图4是实现由外设写FIFO,DSP读取FIFO数据的流程。图中虚线部分表示由dMAX独立完成的工作,实线部分表示由CPU完成的工作。两者之间通过内部中断方式实现状态的交流。

图4 系统软件流程

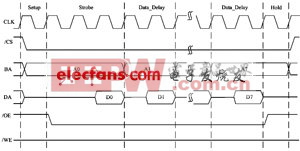

为了提高FIFO的读写速率,一般采用突发方式进行读写。突发方式的读时序如图5所示。写时序和读时序类似。突发方式一次最多只能读写8个数据,也可以一次突发读写4个或者2个数据。突发读写时数据的建立和保持时间最少可以设置成1个时钟周期,如图中所示。但为了通信可靠,一般采用2个时钟周期。突发方式最大的节省时间是连续的其他数据将不再需要建立和保持周期,而是直接进行读写,一般只需要两个时钟周期就可以完成一个数据的读写。最快情况下,突发读写8个数据只需要20个时钟周期,读写速率达到53.2M×32b/s,满足大部分设备的要求。

图5 突发读时序图

总结

dMAX的特有结构使得其可以实现嵌入式FIFO。本文介绍了基于C6727B的dMAX的基本结构以及基于dMAX的嵌入式FIFO软硬件设计,设置通用GPIO引脚作为中断,为了加快FIFO的传输速率,使用突发读写方式进行数据传输。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)