四倍速SRAM与Spartan3 FPGA的接口设计

时间:07-08

来源:互联网

点击:

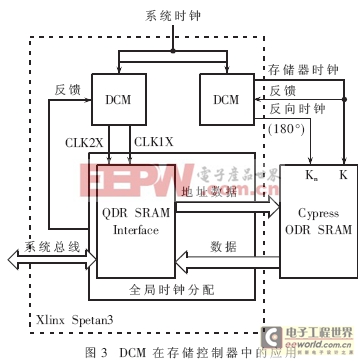

内部全局时钟网络的时钟歪斜,或者消除为片外其他系统组成部分提供时钟的过程中所出现的时钟歪斜。DCM中的DLL能够使控制器完成FPGA的片上时钟和QDR SRAM之间的零时钟歪斜。除此之外,DCM还提供其他的功能,如相位调解,分频和倍频。图3所示为DCM在存储控制器设计中的应用。

- 基于DSP的广播级数字音频延时器(06-07)

- 脱机视频图象编/解码系统中高速DSP芯片应用方案(07-28)

- 一种基于CAN总线与以太网的嵌入式网关经典设计(09-10)

- 在异步SRAM中实现速度与功耗的完美平衡(01-03)

- 针对微控制器应用的FPGA实现(06-06)

- 数字图像倍焦系统设计与实现综合实例之:系统原理框图(06-05)