车载数字视频压缩记录系统设计

于高效、实时的MPEG-1数字图像压缩,且具有功能多、功耗低、温度范围宽等特点。

系统中的SZ1510是从设备,受主机ARM的控制。它的HOST接口是控制和数据交换的接口。SZ1510可以选择多种总线类型,它有复用和不复用的Intel和Motorola总线类型(复用模式下,HAD[7:0]即可作为数据线,又可作为地址线;非复用模式时,HAD[7:0]只能作为数据线),不复用总线又可分为8位和16位,并可由HCONFIG[l:0]引脚和Syscofig[3]寄存器进行选择配置。本系统把HCONFIG0置低,HCONFIG1置高,Sysconfig[3]写1,故可使其工作在Intel 8051类型的非复用16位数据总线模式下。

由于SZ1510有多种工作模式,根据系统要求,本设计使SZ1510工作在LVE(Live Video Encoding)实时视频编码模式。在这种模式下,SZ1510可从视频解码器获得实时数字视频数据,然后根据MPEG1/M-JPEG进行压缩并传到主机。具体工作过程是:SZ1510对输入到其内部的CCIR-601数字视频流经过视频预处理、自动裁减、场景变化检测、运动估计、运动补偿、离散余弦变换/反离散余弦变换和可变长编码等处理后,再将生成的MPEG-1视频基本流存储于SDRAM中,然后经过输出端口大小为256字节的FIFO缓冲进行数据输出。正常工作时,FIFO每满一次就产生一个FRDY (FIFO读)中断以通知主机读取FIFO中的数据,并由主机从Data_out寄存器读取数据。之后,当SZ1510发出一个EOD(数据结束)中断时,数据传输结束。

在视频压缩工作模式下,SZ1510有3种输出比特率可供选择:恒定比特率、最大比特率、可变比特率。恒定比特率需要填充冗余,最大比特率不需要填充冗余,可变比特率的压缩质量比恒定比特率可变。比特率的选择可通过设置Ven_cntl寄存器的1、2位来确定,当其为0时,选择的是恒定比特率;为1时,选择的是最大比特率;为3时,选择的是可变比特率。

2.2 控制及存储电路设计

考虑到控制部分的体积、可靠性和控制能力,本系统中的CPU采用Philips公司的ARM7TD-MI-S内核微控制器LPC2210。这是一个能够支持实时仿真和跟踪的16/32位ARM7TDMI-S CPU。对于代码规模有严格控制的应用,可使用16位Thumb模式,该模式可将代码规模降低30%以上,而性能的损失却非常小。LPC2210采用144脚封装,具有极低的功耗。另外,该芯片还具有多个32位定时器、8路10位ADC、PWM输出以及多达9个外部中断。通过配置总线,LPC2210最多可提供76个GPIO。

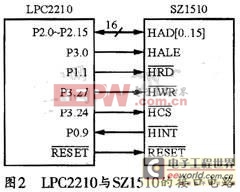

LPC2210可与SZ1510的HOST接口相连,并可通过HOST接口对SZ1510进行控制和设置。正常工作时,LPC2210把从HOST接口输出的MPEG-1格式视频流以文件形式送人电子盘进行存储。LPC2210与SZ1510的接口电路如图2所示。其中,HAD[0…15]接到ARM的P2.0~P2.15A作为16根数据线;P3.0接到HALE脚可实现SZ1510内部IOAR(I/O Address Registerl)和IODR(I/O DataRegister)寄存器的选择;P1.1和P3.27分别接读、写选通管脚HRD和HWR;通过将P3.24接到HCS可选通SZ1510;将P0.9接到HINT可发送SZ1510中断请求信号。

从重量和可靠性出发,本记录单元最终选用电子盘来实现。该电子盘的主体为Flash芯片,该芯片耐冲击,耐高温,体积小,寿命长,适合在汽车环境下工作。虽然电子盘的价格昂贵,但是考虑到系统只采集1路视频信号,记录的数据量也不是很大(计算后得出记录单元的容量为3G时),记录长度可达4.5个小时,所以,选用电子盘完全能够实现任务要求。

LPC2210的GPIO引脚与IDE接口的连接电路如图3所示。图中,P2.16~P2.31为数据线,P1.16~P1.20为地址和选通信号,P0.17和P0.20为设备的复位和状态请求信号,用P0.21和P0.19则可实现读写控制。

3 系统软件设计

本系统的所有软件程序事先均应通过JTAG口烧录到ARM中,这样,系统上电后便可自动运行这些程序以控制系统的工作。系统软件工作流程图如图4所示。

3.1 SZ1510的寄存器配置

SZ1510有128个寄存器,每个寄存器都有一个索引号,外部主机是通过HOST接口(HALE管脚)来设置SZ1510内部的两个寄存器IOAR (I/O地址寄存器)、IODR(I/O数据寄存器)以实现对SZ1510的控制和配置。访问时,首先由主机的A0管脚发送一个低电平到HALE管脚以选中IOAR寄存器,然后将要访问的寄存器索引号写入IOAR;接着由主机的A0管脚发送一个高电平到HALE管脚,以选中IODR寄存器,然后再将要写入的数据写入IODR,这样,SZ1510就会自动把配置的数据送到指定地址的寄存器。

对Z1510进行初始化时,先由主机写任意值到0x0B寄存器;接着在主机至少等待1微秒后,向Int_enable中断使能寄存器写入0x40,以使能RDY(Ready)中断;然后,主机便等待SZ1510的Ready(

- Blackfin助您无线IP视频监控的应用(06-24)

- 基于WinCE的ARM视频监控系统的设计(06-05)

- 解析:视频图像智能分析处理技术(08-08)

- 基于DSP的智能视频监控终端设计与优化研究(09-28)

- 基于DSP芯片TMS320DM642的嵌入式无线视频监控系统设计(01-11)

- 双DSP的多路视频监控系统设计(02-14)