ISA总线实现多路同步DDS信号源设计

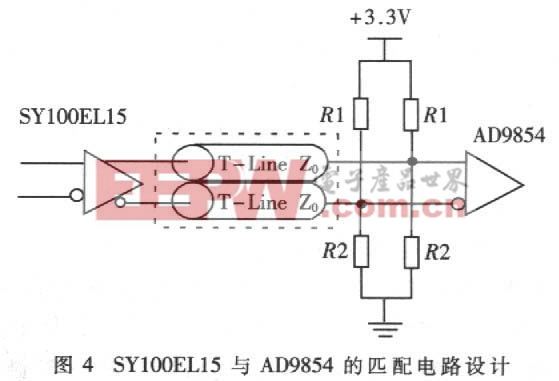

对于3.3V供电的LVPECL电路,R1取126Ω,R2取82.5Ω。AD9854的时钟输入电路有单端方式和差分方式两种,采用差分方式有利于抑制电路产生共模噪声。时钟分配网络布线时,要保证每一路差分时钟信号的走线等长,并且各路DDS时钟信号之间的走线也应当等长。电路板应该按照微带线设计。不同的微带线结构将导致信号传输常数有所差异。 2.2 刷新时钟 AD9854芯片引脚中与配置内核密切相关的信号除了数据线、地址线、写信号以外,还有刷新时钟。写信号的作用是将I/O口上的数据传送到AD9854芯片内部的缓冲区中,而刷新时钟则用于配置AD9854内核的相应寄存器。刷新时钟引脚既可以作为输入信号,工作于外部刷新模式;又可以作为输出信号,工作于内部刷新模式。鉴于多路同步原因,通常工作于外部刷新模式。刷新信号的时序如图5所示。从AD9854内部看,刷新时钟UPDATE实际上是电平有效信号。在该信号出现于AD9854引脚后的第一个系统时钟上升沿,即A时刻,系统时钟识别到刷新时钟。在第三个系统时钟的上升沿,产生AD9854芯片DDS内核的内部刷新时钟。该信号与系统刷新时钟同步,作为将I/O口上的数据配置到AD9854内部配置寄存器的时钟信号。在第四个系统时钟的上升沿,完成对内部寄存器的配置。在第五个时钟的上升沿,产生内部刷新时钟信号的下降沿,配置过程结束。以图5为例,为使该过程工作可靠,应当保证三路DDS芯片的刷新时钟必须超前于相同的系统时钟,即时钟0,否则会导致各路DDS的输出相差一个AD9854的系统时钟。 2.3 锁相倍频 根据数模转换的数学模型,DDS输出信号的频率通常不得超过系统时钟频率的40%。以50MHz作为参考时钟产生频率为20MHz的信号会给滤波带来困难。AD9854内部集成了锁相倍频电路,可以将50MHz的参考时钟倍频至200MHz。片上锁相倍频电路带来的问题是环路建立时间会随着AD9854及片外环路滤波器的器件不同而产生差异。这将导致在锁相环路的建立过程中,送给AD9854相位累加器的系统时钟周期数目无法准确预测。因此在环路建立过程中,相位控制字的值必须为零以避免相位累加器的值不断累加。DDS芯片内部集成锁相环路的建立时间典型值约为400μs。为了保证各路DDS的同步,在起始10ms让AD9854输出的频率控制字和相位控制字始终为零。10ms以后,才启动AD9854的输出相位累加过程。待PLL建立起来以后,再改变各路DDS芯片相应的控制字。 计算机的主控软件用VB语言编写,系统FPGA软件用VHDL语言编写。FPGA内部设计了一个基于FIFO技术的缓冲区,将主控计算机发送过来的各类控制命令暂存。为了简化控制时序,采用的方法是利用ISA总线的数据线依次传输各路AD9854的配置数据和寄存器地址,并且暂时存放在缓冲区中;而后利用ISA总线的写信号作为各路AD9854的刷新时钟信号,完成对DDS芯片的同步配置。 3 测试结果 ISA总线信号源采用四层印刷电路板设计。布线时,采取电源退耦滤波、合理分割内电层、隔离数字地和模拟地等措施,有效地克服了计算机内部复杂的电磁干扰环境,得到了较好的测试结果。结果表明,信号在20MHz处的相位噪声优于一100dBc@lkHz,在O~0.5fs范围内的杂散抑制优于-55dBc。以DDS的尉新信号作为同步参考信号,三路DDS(包括DDS3的I/Q两路),从刷新时钟上升沿到DDS有信号输出,时间间隔均为305ns,能够实现精确的同步。 本文对基于计算机的DDS技术做了尝试。在没有增加屏蔽结构的条件下。频率合成器的相位噪声和杂散指标都满足系统要求,针对AD9854,通过精心设计,实现了多路DDS的同步和IQ正交输出。

- 基于DSP和CPLD的宽带信号源的设计(07-26)

- 基于DDS+PLL的X—Band信号源设计(10-14)

- 基于TMS320F2812的变频调压功率信号源设计(10-28)

- DSP和DDS的三维感应测井高频信号源实现(01-23)

- 基于AT89LV51控制的DBPL编码信号的信号源系统(01-23)

- 基于FPGA的TFTLCD快检信号源的设计(06-06)