基于SOPC的车辆息线控制器设计方案

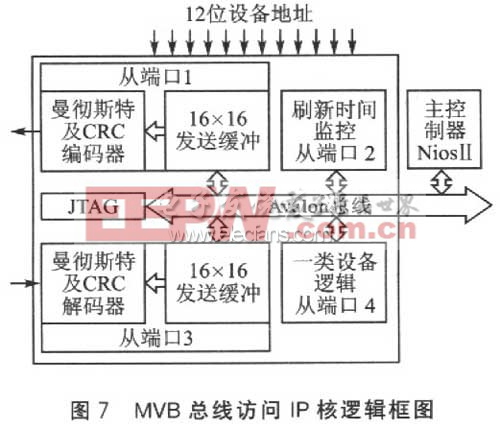

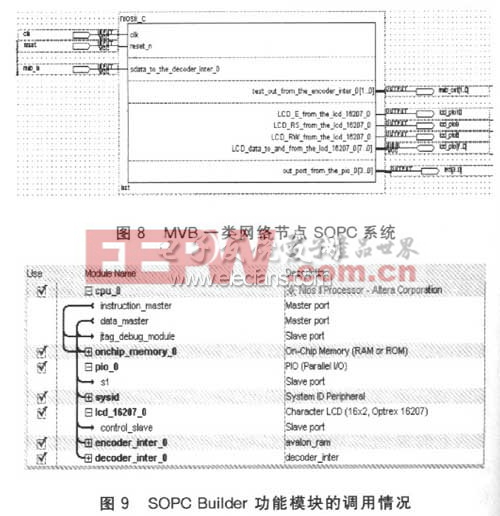

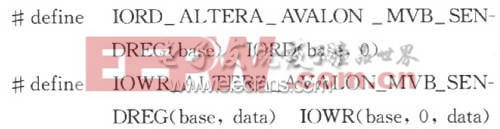

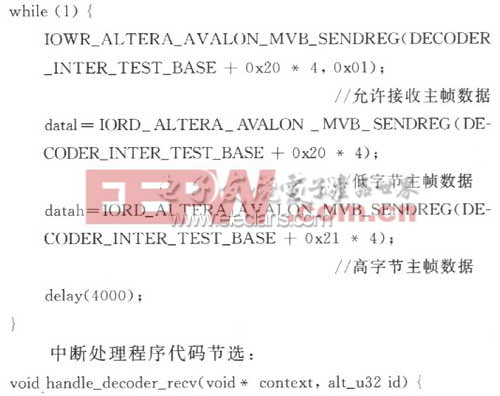

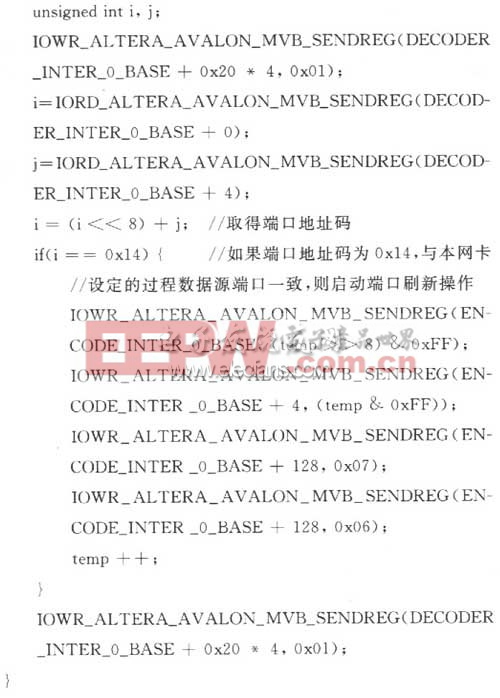

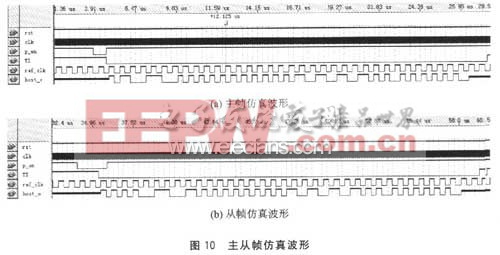

如图7所示。 3 SOPC片上系统MVB控制器设计 3.1 总线访问IP核与NiosII的系统集成 利用QuartersII的SOPC Builder工具,集成了1个32位NiosII软核处理器、4 KB的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,在Altera的CycloneII FPGA上构成了一个能实现MVB一类网络节点功能的片上系统,如图8所示。图9为SOPCBuilder中各个功能模块的凋用情况。 基于上述SOPC系统,设计了一个基本的MVB节点,以实现过程数据传输。该节点将Oxl4地址设置为源端口。当主帧轮询0x14地址时,本节点将此端口里的数据打包成从帧发送到总线上面,以刷新0x14地址的宿端口。 MVB模块头文件altera_avalon_mvb.h的设计,包括总线访问IP核寄存器读写的宏定义。 在主函数里置MVB总线接收允许位,循环等待接收MVB主控制器发过来的主帧。节点在接收到主帧之后,程序进入中断处理程序。在巾断程序里提取接收到的主帧里的端口地址,并与自身预设的端几地址码进行比较。如果地址码相符,则节点将本端口的数据通过MVB发送器发到总线上,实现端口数据刷新操作。 主循环代码节选: 4 仿真与实测波形 4.1 仿真波形 在本实验中,对实验室设计的MVB板卡进行了功能仿真和FPGA验证.通过对过程数据的发送与接收验证了所搭建的MVB系统。对MVB总线控制器发送过程的主从帧仿真结果如图10所示。发送的主从帧数据都为0x0055,包含1个帧头及8位CRC校验数据。 4.2 实测波形 编好程序后,再编译一遍QuartersII工程文件,将得到的.pof文什下载至FPGA内。上电后用示波器测输出引脚,便可观察到MVB从帧波形,实测波形如图11所示。对照IEC-61375协议标准,可以判断出该渡形为符合标准的正确波形,并且源端口节点上收到了正确的数据,从而证明该过程数据端口成功刷新。 结语 目前,MVB控制器实现了实验室环境中过程变量的正确接收和发送。本总线访问IP核实现的功能与MVBC相当,但是由于采用了先进的SOPC设计技术,其体系结构大大简化,设计难度也大大降低,在通用性方面有了很大的提高。

3.2 NiosII处理器上的软件设计

3.2 NiosII处理器上的软件设计

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)