基于DSP和FPGA的多波形雷达回波中频模拟器实现

b的双口RAM也可借助片外双口RAM实现,降低对FPGA存储资源的依赖。该方法的缺点是有更大的固定延迟,虽在延时大时可预先由DSP修正控制值,但对要求延时小于其固定延时的情况则无法适用。本系统综合采用两种方法解决,即:DSP输出码值的最高位决定延时方法的切换,当需求的延时大于固定延时时则采用图4的方法;而需求的延时小于固定延时时采用图2的寄存器法。

3.2 数字噪声基带产生模块

本系统噪声基带信号的产生采用数字技术,在FPGA内完成,实现方法如图5所示。

根据随机信号理论,对均匀分布的随机数进行白化处理,可实现具有良好统计特性的高斯白噪声。系统首先采用2个独立的m序列发生器产生[0,1]区间上均匀分布的伪随机数,m序列发生器的硬件结构如图6所示,其中Co和Cn为对应m序列多项式的系数,取值为0和1。

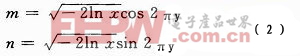

然后将产生的一对伪随机数通过Box_Muller变换可以得到一对相互独立的符合标准正态分布的伪随机数m和n,正好作为噪声产生器的同相分量和正交分量。Box_Muller变换公式为:

式中:x,y即为前述2个互相独立的在(0,1)上均匀分布的伪随机数。

由于Box_Muller变换需要用到两个非线性函数,而非线性运算很难在实际数字电路系统中实现,故实际中需要构建相应查找表实现非线性运算,分别记作sqrt_lut和sincos_lut。设sqrt_lut和sincos_Iut的输出量化数据长度为L1和L2位,独立变量m和n的定点长度分别为N1和N2位。则当采用均匀量化方案时,sqrt_lut和sincos_lut所需的存储空间分别为2N1×L1和2N2×L2。可以看出,如果直接实现查找表功能,当N1和N2较大时,对应的存储空间是相当可观的。

为了压缩存储空间,对sincos_lut,可以只存储第一象限的正余弦值。其他象限则通过符号调整得到,这样可以将sincos_lut占用存储空间减少到原来的1/4。更进一步,还可以对非线性曲线进行分段折线近似,在实际查找表中只存储各折线段的起始位置及对应斜率。也可以大幅度减少所需查找表的数量,该策略同样适用于sqrt_lut查找表。

得到一对相互独立的符合标准正态分布变量m和n后,还要对其进行低通滤波,以适应对应的信号带宽。由于I路与Q路的滤波特性完全相同,为进一步节省资源,可采用一个支持双通道操作的滤波器同时完成I路与Q路的滤波。这可以通过ISE集成开发环境中Core Generator中的FIR IP核来方便实现。滤波器系统可由上位机根据所需带宽,传递相应系数给DSP,继而传递给FPGA。

噪声功率调整模块可根据设定信噪比的不同,乘以相应系数,对产生的带限高斯白噪声幅度进行调整。

4 结论

本系统基于自主产生的原理,选用DSP和FPGA为核心处理器,通过合理的算法设计,实现了可兼容多种雷达波形的中频雷达回波模拟器的设计,采用改进的基于存储转发的数字脉冲延时方法,在达到8 ns的最小延时步长的同时,降低了对系统的硬件要求。系统的另一个关键模块是数字噪声发生器,其参数可以进行实时修改,极大地提高了噪声发生器的灵活性,与其他同类型设计相比,具有工作速度快,资源利用率高,硬件结构简单等特点。最后采用DDS、数字正交上变频等器件,实现了精确的复杂频率调制、相位调制和幅度调制,保证了系统的灵活性、高兼容性和集成化程度。

中频 模拟器 实现 雷达 波形 DSP FPGA 基于 相关文章:

- 基于DSP的中频电源测试系统设计(08-08)

- 基于FPGA+DSP的高速中频采样信号处理平台的实现(03-25)

- 基于DSP_C54X窄带中频抽样的理论与实现 (07-06)

- 基于DSP、DDS和ARM雷达中频信号模拟器研究(05-18)

- 基于ADSP21535的中频信号产生器在雷达MTI改善因子测试中的运用(09-16)

- 基于PLC的中频逆变电阻点焊机研制(12-15)