FPGA芯片结构分析

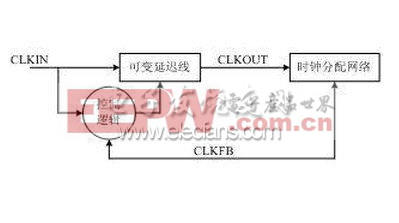

资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片 Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有密切、直接的关系。6. 底层内嵌功能单元内嵌功能模块主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等软处理核(SoftCore)。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC平台过渡。DLL和PLL具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。Xilinx公司生产的芯片上集成了 DLL,Altera公司的芯片集成了PLL,Lattice公司的新型芯片上同时集成了PLL和DLL。PLL 和DLL可以通过IP核生成的工具方便地进行管理和配置。DLL的结构如图1-5所示。图1-5 典型的DLL模块示意图

典型的DLL模块示意图7. 内嵌专用硬核 内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(Hard Core),等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:为了提高FPGA的乘法速度,主流的FPGA 中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。 Xilinx公司的高端产品不仅集成了Power PC系列CPU,还内嵌了DSP Core模块,其相应的系统级设计工具是EDK和Platform Studio,并依此提出了片上系统(System on Chip)的概念。通过PowerPC、Miroblaze、Picoblaze等平台,能够开发标准的DSP处理器及其相关应用,达到SOC的开发目 的。

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 关于Linux操作系统的NTFS和内核分析(05-19)

- Linux 2.4.x内核软中断机制(04-06)

- 基于DSP的人脸识别系统设计(04-26)

- 3D图形芯片的算法原理分析(07-16)

- 解析:视频图像智能分析处理技术(08-08)