多通道实时CAN模拟器设计方案

因此,单片机与CAN控制器之间的锁存、译码采用Xilinx公司XC95144CPLD芯片,优化了系统资源,降低了其功耗。

2.2 系统硬件设计

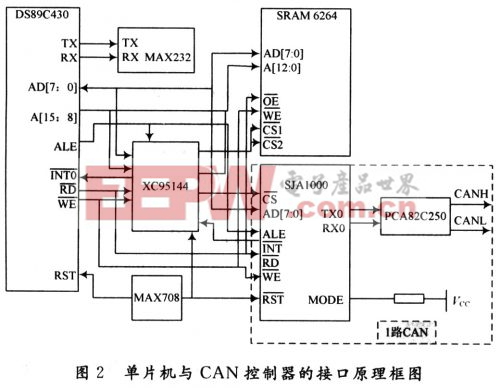

该部分由单片机、CAN控制器、CAN收发器、SRAM存储器组成。单片机主要用于系统计算及信息处理等功能;CAN控制器主要用于系统通信;CAN收发器主要用于增强系统的驱动能力;SRAM主要用于缓存数据。系统的发送过程是:单片机将外围设备传送过来的信息处理后,按CAN规范规定的格式,将其写入CAN控制器的发送缓冲区,并启动发送命令,把数据发送到CAN总线上;接收过程是:CAN控制器从CAN总线上自动接收数据,并经过滤后存入CAN接收缓冲区,且向单片机发出中断请求,此时单片机可从CAN接收缓冲区读取要接收的数据。SJA1000提供的微处理器接口方式为典型INTEL或MOTOROLA地址数据多路复用总线模式。主要信号有地址数据信号AD7~AD0,地址选通信号ALE,片选信号CS,读信号RD,写信号WR,模式选择信号MODE。当MODE=1时,为INTEL模式;当MODE=0时,为MOTOROLA模式。后面描述的总线模式均为INTEL模式。AD7~AD0引脚在ALE有效时,传送的是地址信号,在RD或WR有效时,传输的是数据信号,在这里分别与单片机的PO口相连,RD,WR信号线分别与单片机的读/写信号线相连。具体方案如图2所示。限于篇幅限制,虚线内给出1路CAN的连接图,2路CAN有同样的连接方法。

SRAM和CAN控制器的片选信号。由于单片机可以查询或中断方式访问,在此采用中断方式进行CAN多通道选择访问,以满足不同通信速率下数据处理的需要。SRAM的地址线与数据线是分开的,故采用74LS373锁存器实现锁存功能。可采用XC95144CPLD芯片以及VHDL硬件描述语言以实现锁存、译码等功能。

2.3 CPLD设计部分

2.3.1 结构设计

CPLD的输入信号是单片机发送的信号,由高位地址A[15..8]、ALE锁存信号、中断信号以及写/读信号组成。地址线A14和A15经译码后作为片选信号,ALE实现低8位地址线的锁存。实体和构造体部分代码如下所示:

2.3.2 仿真结果

该模块在Xilinx ISE 9.1工具下进行综合,并在结合ModelSim环境下进行功能仿真。其仿真结果如图3所示。

3 软件设计

该系统软件设计的关键是通信程序设计。通信软件由三部分组成:单片机和CAN控制器的初始化程序、CAN发送程序、CAN接收程序。对于初始化程序,采用MAX232芯片对单片机进行在线编程,可同时对多通道CAN控制器初始化。对于CAN控制器的初始化程序,主要是通过对CAN控制器控制段中的寄存器写入控制字,从而确定CAN控制器的工作方式等,即通过上电复位、硬件复位或软件复位给CAN控制器发一个复位请求,便可进入初始化。在复位期间,对必需的寄存器进行设置。对于发送和接受程序,只需把到来的信息帧送到CAN的发送或接受缓冲区,同时启动命令即可。二者可采用查询方式或中断方式,对于中断方式,程序分为主程序和中断服务程序两部分设计。在具体项目中,需要软硬件结合调试才能保证各部分的设计准确无误,到达实际应用的要求。

4 结 语

在对CAN通信协议进行分析的基础上,构建了一种多通道实时CAN总线模拟器架构,同时利用CPLD器件,通过功能仿真,验证了设计方案的正确性。经实际工程项目使用,验证了该设计方案切实可行,满足了实际应用中高可靠性、高实时性以及传输速率较高的需求。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)