基于FPGA的SoC验证平台实现电路仿真侦错

时间:09-13

来源:互联网

点击:

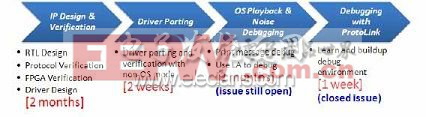

解决音效问题,同时也在音效驱动程序中增加观察点,以连结并企图找出问题。这种传统的FPGA侦错方法,需要的时间和设计研发的时间一样长,然而对工研院团队而言,相当令人沮丧的是结果仍然一无所获。不过,在经过思源科技提供的应用软件教育训练/支持课程及一星期的实作经验后,工研院工程师使用ProtoLink Probe Visualizer,在短短一星期的时间内就厘清了两大问题!

对工研院而言,ProtoLink Probe Visualizer是一种相当有效的FPGA原型板侦错方法。工程师再也不必局限在传统的侦错方法,而且在实时应用软件中增加观察点也可能会造成其它问题。透过维持原有软件并监测更多FPGA讯号在数百万时脉周期内的实时RTL行为,使用者可以获得所需的能见度,更完美的掌握、更轻松地侦错设计的问题。

总合来说,思源科技Probe Visualizer透过以软件为基础的创新方法,改变了原型板验证的方法,实现丰富、实时的设计能见度,并且让原型板能使用Verdi的侦错威力,使原型板侦错时间比传统的方法大幅缩短一半。

实现 电路 仿真 平台 验证 FPGA SoC 基于 相关文章:

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)