用一个时钟在FPGA中计算直方图

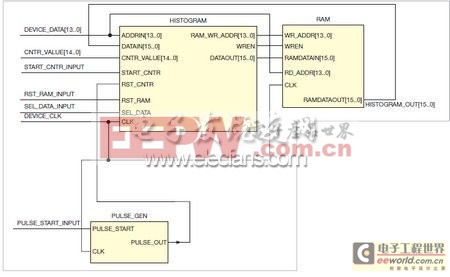

直方图对数字数据的分析通常是一种有用的工具。不过,要从一个直方图获得可靠的结果,必须获得大量数据,通常是要10万到100万个点。如果需要分析一个ADC的数字输出,可以采用一片FPGA(图1)。

图中显示了直方图、RAM和脉冲发生器部分,用于捕捉和显示基于14 位数据计算出来的直方图。RAM块是FPGA的内置RAM,而直方图块是用于计算的VHDL(高级设计语言)代码。 来自ADC的14 位并行数据Device_ Data[13..0]进入直方图块,并进入RAM的Rd_Addr输入端。RAM在其地址位置RAMDataOut[ 15..0]上提供数据。这个数据环回到直方图块,将其加1后送至一个16 位数据的输出端DataOut[15..0]。当WREN(写使能)端为逻辑电平1时,数据被写在管脚Wr_Addr[13..0]处的地址。这种方法与数据来自Device_Data[13..0]是相同的。

RAM从输入到输出有一个固定的延迟。即,当输入为Rd_Addr时,经过一个固定延迟后,数据出现在其输出端RAMDataOut。这个延迟随不同FPGA而改变。要注意这个延迟,使得有两个时钟的延迟到Device_Data,然后再计算直方图。RAM中的延迟应小于两个时钟周期;否则,就可能有数据丢失。这个约束限制了Device_Clk的最大频率。

Cntr_Value给出了用于计算直方图的输入数据数量。Pulse_Gen块产生一个脉冲,进入输入端Rst_Cntr,用于复位计数器。此时,直方图部分再次用Cntr_Value的下组输入数据计算直方图。Cntr_Value为15 位,但可以增加它,获得更多的直方图数据。

Sel_Data与Rst_RAM信号是重置在FPGA RAM中存储的数据。当Rst_RAM脚出现高信号时,直方图块的DataOut脚的所有位均为0。当直方图块的Sel_Data输入脚为高信号时,RAM_Wr_Addr的输出不是Device_Data,而是一个从0上升至16384的内部生成的斜波。直方图块不做计算,因为这样做会重置RAM的地址。

图1,直方图计算电路从一个FPGA的RAM块中获取数据。

当FPGA完成了直方图计算时,RAM就可以选择Sel_ Data为逻辑高,而将保持Rst_ RAM为逻辑低,从而读取直方图数据。RAM地址中的数据顺序地退出输出脚,并且可以将数据传输给一台PC。由于所有块都以一个单时钟Device_Clk工作,因此本设计很简单,有助于满足时序的约束。可以方便地修改本设计,从而获得16 位或12 位数据直方图。

FPGA 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)