基于FPGA原型设计 能为您做些什么?

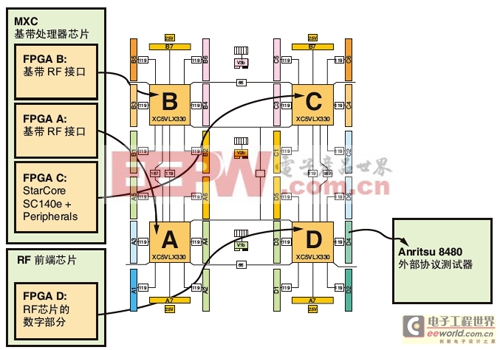

括硬件驱动程序、操作系统和协议栈代码。虽然如前所述主要的目的是协议测试,通过使用 FPGA,所有这些软件开发工作都能够在流片前完成,从而大大加快各种最终产品的开发进度。 Freescale 构建了一个多芯片系统的原型,其中包括一个双核 MXC2 基带处理器和一个 RF收发器芯片的数字部分。基带处理器内置一个用于调制解调器处理的 Freescale StarCore DSP内核、一个用于用户应用处理的ARM?926 内核,以及 60 多个外设。 Synopsys HAPS-54 原型板用来实现原型(如图 3 所示)。该基带处理器有 500 多万个 ASIC门,Scott 的团队使用 Synopsys Certify 工具将其在原型板上划分给三个赛灵思 Virtex-5FPGA,同时把数字 RF 设计布置在第四个 FPGA 中。Freescale 决定不构建模拟部分的原型,而是直接从 Antritsu协议测试盒中以数字形式提供移动网络数据。 较早的内核使用的某些设计技术对ASIC 来说非常有效果,但对 FPGA 来说却不太好用。另外,RTL 的一部分是从系统级设计代码中自动生成的,由于其过于复杂的时钟网络,对 FPGA 来说也是相当不利。因此,必须对 RTL 进行一些调整,使其更加兼容 FPGA,这样做的成效非常显著。 除了能够加快协议测试, 到Freescale 的工程师完成首个芯片时,他们还能够: 仅在完成首个芯片后一个月,Freescale 团队就成功地从这个系统中拨出了第一个移动电话呼叫,把产品开发进度缩短了6个多月,这非常具有里程碑意义。 如 Scott Constable 所说,“除了加速我们所述的协议测试目标外,我们的 FPGA 系统原型还加快了众多其他领域的项目进度,再次证明了它的价值。 也许最重要是给开发人员带来的不可估量的好处:它能够让工程人员尽早参与项目,让从设计到软件到验证再到应用 “ 鉴于如此多的优势, 用基于FPGA 的原型解决方案来加快 ASIC 的开发进程是一件非常自然的事情。我们随后将这种方法介绍给了 Freescale 网络和微控制器部,还将其用于最新 IP验证、驱动程序开发、调试器开发和客户演示。” 这个例子说明基于 FPGA的原型方法能够给软件开发团队提供什么样的增值工具,能够在产品质量和项目进程方面带来怎样显著的回报。 接口优势:测试真实条件下的数据效应很难想象有这样一种 SoC 设计可以不遵守输入数据、处理数据、生成输出数据的基本结构。实际上,如果我们深入 SoC 设计,就会发现无数的子模块遵循着同样的结构,直到单个门级。要在这些层级中的每一个层级验证正确的处理,要求我们提供完整的输入数据集,并观察处理结果的输出数据是否正确。对单个门来说,这个工作很简单,对小型 RTL 模块来说,也是可能的。但随着系统日趋复杂,从统计上来说基本没有可能确保输入数据和初始条件的完整性,尤其是在有软件运行在一个以上的处理器的时候。 为了提升传统验证方法的效率和覆盖面,以及应对这种复杂性所带来的挑战,我们已经投入了大量的研究工作和资金。在完整的 SoC 层面,我们需要使用多种不同的验证方法来覆盖所有输入组合并和剔除极端情况下的组合。 最后一点非常重要,因为不可预测的输入数据能扰乱所有的 SoC 系统,即便是精心设计的关键SoC设计也难以幸免。与新输入的数据或者输入数据不寻常的组合或序列相结合的,是非常多的 SoC 可能的前置状态,可能会使SoC 处于某种无法验证的状态。当然,这种情况不一定是什么问题,SoC 可以在无需系统的其他部分干预的情况下恢复,或者用户根本就没有察觉。 但是,不能验证的状态必须在最终芯片中避免,因此我们需要尽可能全面地测试设计的方法。在设计的功能仿真过程中,验证工程师会采用有力的方法,比如受约束随机激励和高级测试工具来完成多种测试,旨在达到可接受的测试覆盖面。但是,完整性仍受验证工程师选择的方向和给定的约束条件的限制,并受限于可用于运行仿真的时间。 结果虽然受约束随机验证永远不可能穷尽,但能够大大增强我们已经测试了所有输入的组合(包括可能的输入和极端 为了屏蔽极端情况下的组合,我们可以通过观察真实条件下运行在基于FPGA 原型上的设计来完善我们的验证工作。通过将 S

?发布调试器软件,且在芯片实现后无需进行大的修改;

?完成驱动程序软件;

?在操作系统提示符下引导SoC;

?实现调制解调器阵营(modem camp)和注册。

的所有开发团队在芯片完成前半年时间内就对产品了如指掌。这种对产品专业知识认知的进程的加快是难以用甘特图

(Gantt chart) 来衡量的,却可能是最有益处的。”

情况输入)的信心。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)