FPGA实现视频广播接收系统方案

1.DM9101

DM9101是一个物理层的、单片、低功耗的100Base-TX和10Base-T操作的转换器。在介质这一边,它既为用于100Base -TX快速以太网的非屏蔽双绞线对(5类同轴电缆)提供一个直接的接口,也为用于10Base-T以太网的UTP5/UTP3提供直接的接口。通过 IEEE802.3u介质无关接口(MII),DM9101可以与介质接入控制(MAC)层相连接,确保了在不同生产商的产品之间的高度互操作性。

该芯片集成了MII标准接口、100Base-TX发送/接收器、10Base-T发送/接收器、自动协商、冲突检测、载波侦听、4B5B编/解码器、加/解扰器、串口和并口之间的转换等功能。

由于采用了MII标准接口,使得设计者可以通过该接口的管理信号线对该芯片的寄存器进行设置,从而完成对10 Mbps和100 Mbps两种速率的选择,突出了设计的灵活性。

2.FPGA设计

由于要使数据能在以太网上传输,服务器端的发送程序应该把要传输的数据进行打包(或封装)。本系统中所要传输的数据为视频数据(VCD数据),而VCD数据一般是以dat格式存放在光盘中的。因而在接收端应对接收到的数据包进行解包,并同时完成数据格式转换的功能,使得送到MPEG-1解码芯片的数据格式为dat格式的数据,从而进行解码,最后用普通的电视机就能够接收。

因而该部分主要要实现的功能是:先完成对接收到的以太网数据帧进行解包,取出封装在以太网数据帧中的数据部分,然后再分别解IP数据包和UDP数据包,把真正的具有VCD播放格式的数据取出来,经过一个先进先出(FIFO)缓冲器输出到MPEG-1解码芯片进行解码。其中在解包的过程中,要对数据进行校验,校验正确的数据包才进行传送,对于校验不正确的数据包采用了直接丢弃的方法,所采用的校验算法是循环冗余校验算法(CRC)。

设计框图如图3所示。

(1)前导检测:当系统检测到连续出现了15个nibble的1010,同时随后的一个nibble为1011时,说明一个以太网数据帧开始了,应该对该部分的数据作进一步的处理。

(2)组字节:由于从DM9101芯片出来的数据信号是以一次四位元组(nibble)的形式传输的,因而要对它进行组字节操作,每2个nibble组成一个字节,具体操作过程依据的是MII帧结构中的字节组成格式进行。

(3)CRC校验:对以太网帧中的目的地址、源地址、长度、数据进行CRC校验,并与帧的最后四个字节进行比较,如果一致,即为正确的以太网数据;若不一致,则丢弃这一帧。

(4)MPEG-1数据:取出以太网帧中的长度字节的值,用这个值来预置一个计数器,从而对数据进

行计数控制,取出其中的MPEG-1格式的有效数据。

(5)FIFO:由于普通的以太网的数据传输速率是10

Mbps或100 Mbps,而进行MPEG-1解码时的速率一般为1.5 Mbps左右,因而要对数据流进行速率调整。该FIFO直接利用了Spartan II系列芯片内部的存储模块进行缓存。

(6)同步头检测:dat格式的数据帧有一个同步头为:00FFFFFFFFFFFFFFFFFFFF00(十六进制),当检测到该同步头时,表明一个dat数据帧开始了,应将其后的数据连同该同步头信息一起输出至解码芯片。

(7)串行输出:把最后得到的数据转换为串行数据,并以I2S的格式将数据和时钟等信号输出到 MPEG-1解码芯片中进行解码。

四、仿真结果

1.组字节仿真结果

数据从2个nibble组成一个字节的仿真结果如图4所示。其中,CLK信号是25 MHz的时钟信号,DA是由4位数据组成的数据信号,它们由DM9101芯片输出;DATA为组成字节后的8位数据信号,CLK—B是由CLK信号二分频所得到的Byte时钟信号。

2.I2S格式仿真结果

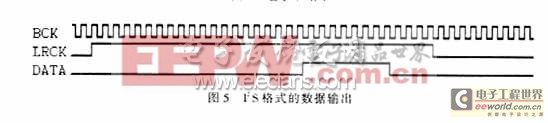

以I2S格式输出的数据的仿真结果如图5所示。仿真中采用的格式是:32位BCK,MSB最先,右通道为低电平。其中BCK是位时钟信号,LRCK是左右时钟选择时钟,DATA是VCD格式的MPEG-1视/音频数据。

五、小 结

本系统所采用的FPGA芯片为Xilinx公司的Spartan II系列芯片,用Foundation软件工具开发。设计输入完成后,进行整体的编译和逻辑仿真,然后进行转换、布局、延时仿真生成配置文件,最后下载至 FPGA器件,实现其硬件功能。由于系统的很多功能由一块FPGA实现,外围器件很少,所以系统体积小、可靠性高,且器件的可编程性使得系统功能易于完善。仿真结果表明,各信号的逻辑功能和时序配合完全达到了设计要求。

以太网 相关文章:

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- TM1300 DSP系统以太网接口的设计(03-07)

- 工业级特性在嵌入式处理中至关重要(05-08)

- 基于VxWorks的双端口网卡智能双冗余驱动(07-01)

- 基于μC/OS-II和TCP/IP协议的多串口服务器(08-23)

- 基于DSP/FPGA的以太网控制器的运动控制器设计(02-06)