DDS芯片AD9850的工作原理及其与单片机的接口分析

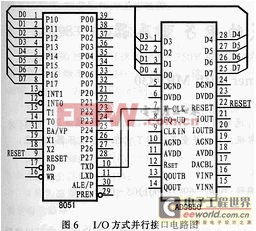

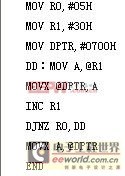

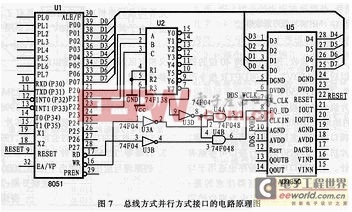

业控制领域。单片机由芯片内仅有CPU的专用处理器发展而来。最早的设计理念是通过将大量外围设备和CPU集成在一个芯片中,使计算机系统更小,更容易集成进复杂的而对体积要求严格的控制设备当中。INTEL的Z80是最早按照这种思想设计出的处理器,从此以后,单片机和专用处理器的发展便分道扬镳。 3.1 I/O方式并行接口 I/O方式的并行接口电路比较简单,但占用单片机资源相对较多,图8是I/O方式并行接口的电路图,AD9850的数据线D0~D7与P1口相连,FQ-UD和W-CLK分别与P3.0(10引脚)和P3.1(11引脚)相连,所有的时序关系均可通过软件控制实现。 将DDS控制字从高至低存放于30H至34H中,发送控制字的程序清单如下: 在程序中,每将一字节的数据送到P1口后,必须将P3.1(W-CLK)置高。在其上升沿,AD9850接收到P1口相连的数据线上的数据,然后将P3.1置低,并准备下一字节的发送,连续发送5个字节后,须将P3.0(FQ-UD)再次置高,以使AD9850根据则输入的控制字更改频率和相位输出,随后再置P3.0为低,准备下一组发送。单片机的P3.0、P3.1引脚为串行口,当被占用时,W-CLK和FQ-UD引脚也可与其它I/O脚相连,这时需要修改相应的发送程序。 3.2 总线方式并行接口 总线方式并行接口占用的单片机资源较少,在这种方式下,AD9850仅作为一扩展芯片而占用RAM的一段地址,必须时也可以只占用一个地址。图7是总线方式并行接口的电路原理图。同样将DDS控制字从高至低存放于30H至34H中,发送控制字的程序清单如下: AD9850的W-CLK和FQ-UD信号都是上升沿有效,用MOVX @DPTR,A指令向AD9850传送控制字时,由74F138将高八位地址的低三位译码,其输出经反相并与反相后的信号相与得到一上升沿送至AD9850的W-CLK脚,此时已送到总线上的数据将被AD9850接收,连续五次将40位的控制字全部发送以后,用MOVA A,@DPTR指令产生FQ-UD信号,使AD9850更改输出频率和相位,此时读入到单片机内的数据实际上无任何意义。图7中AD9850的地址为0700H。 上述两种接口方式经实际应用证明:工作可靠,效果良好。单片机与AD9850的串行接口可参照有关资料进行设计。上述接口电路和程序也适用于与AD9850脚对脚兼容的AD9851,值得注意的是:AD9851的控制字与AD9850控制辽中别位的定义稍有区别,编程时应予以注意。

单片机 接口 分析 及其 原理 芯片 AD9850 工作 DDS 相关文章:

- FPGA的DSP性能揭秘(06-16)

- 基于单片机通用引脚的软件UART设计(10-16)

- 分时操作系统思想在单片机中的具体应用 (10-30)

- 基于AT89C51+DSP的双CPU伺服运动控制器的研究(05-26)

- 关于RTX51 TINY的分析与探讨(05-30)

- 基于MC9S12DGl28单片机的智能寻迹车设计(04-03)