基于CPCI总线的测井数据采集板卡的设计

时间:10-20

来源:互联网

点击:

脉冲信号的数量体现测井设备在井下的深度,此信号是测井系统的重要信号之一,如果测量不准, 可能会导致测井资料作废, 甚至带来生产事故。实测Encoder信号从井下设备传送到地面时,会有尖峰脉冲干扰引入,所以本板卡在硬件上采用RC无源滤波器去除信号的尖峰脉冲,通过FPGA在软件上对信号进行去抖动处理、计数和相位判断,能够准确计数并与系统时钟同步。

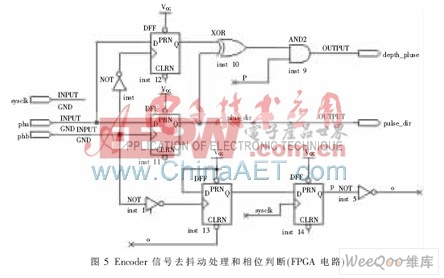

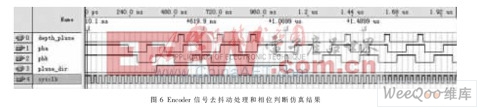

FPGA中对Encoder脉冲信号的去抖动处理和相位判断设计电路见图5,其中depth_pluse为去抖动后的脉冲信号,结合depth_dir完成脉冲计数,当depth_dir为正时,计数脉冲自加,depth_dir为负时,脉冲计数自减。本文用QUARTUS软件自带仿真工具对Encoder信号做的仿真波形,见图6,如波形所示,在时间节点619.9 ns、1.069 9 μs和1.489 9 ?μs处分别对A信号和B信号加入了干扰脉冲,但结果表明本设计可以对干扰脉冲完全滤除。

本文给出了一种高性能测井数据采集板卡的设计方法,板卡在设计中,模拟部分采用多级滤波、高精度A/D,使得数据采集稳定可靠,Encoder深度脉冲信号在硬件滤波的基础上做了软件优化处理,明显增强了抗干扰能力,数字部分采用FPGA和DSP相结合,使板卡具有很高的灵活性、可靠性和可升级性。经大量测试,板卡运行稳定,并在实际系统中得到应用。

- 基于DSP的CPCI总线架构设计的实时图像信号处理平台(03-27)

- 一种CPCI总线结构微波接收机的设计方案(12-21)

- 一种基于CPCI总线的智能故障信息系统子站(12-20)

- PCI IP核在CPCI总线数据采集卡的应用设计(12-15)

- SOPC在PCI总线高速数据传输系统中设计应用(12-12)

- CPCI总线技术在加固计算机的开发平台中的应用(01-11)