DSP芯片与A/D转换器和D/A转换器接口的设计

MAX153和MX7545是美国MAXIM公司近几年推出的8位A/D转换器和12位D/A转换器。MAX153具有高达1MSPS的采样率,MX7545具有4MSPS的数/模转换速度。

MAX153和MX7545可以很容易地与一般微处理器接口,而不需要过多地考虑时序问题。然而,当它们同时与高速数字信号处理器(DSP)接口时,就需要从软硬件的设计上仔细考虑时序问题和其它问题。

下面先简单介绍一下MAX153和MX7545的工作模式,随后以它们与TMS320C30数字信号处理器的接口为例,详细介绍接口的软硬件设计方法。

1 MAX153的工作模式

根据MODE管脚上信号的不同,MAX153有两种不同的工作模式。当MODE接地(0V)时,转换器处于RD工作模式;当MODE接高电平(+5V)时,转换器处于WR-RD工作模式。限于篇幅,下面将只介绍WR-RD工作模式。

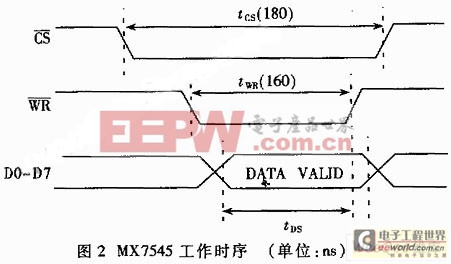

从图1可以看出,转换器在WR的下降沿开始启动,当WR变高时,高4位的数据已转换完毕且已送到输出缓冲器,同时低4位数据开始转换,380ns后INT变低,表明低四位数据转换也已完成。数据的读取有两种方式,这里仅介绍最快工作模式下的数据读取方式。

图1所示的是由外部信号控制的转换时序图。在这种读取数据的模式中,RD信号提前有效,可以获得最快的转换时间。一般RD在WR的上升沿250ns后变为低,就可以完成转换获得数据。INT在RD的下降沿变为低,之后,随着RD或CS的上升沿而变为高。

2 MX7545的工作模式

与一般的D/A转换器一样,MX7545也有电流和电压两种工作模式。其中,电流工作模式又分为单极性和双极性两种,这里只介绍单极性电流工作模式。

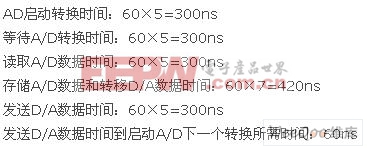

不论是电流工和模式还是电压工作模式,MX7545的工作时序是一样的,如图2所示。其中,MX7545在一个转换周期内,片选信号CS有效时间tcs需要180ns,写信号WR的有效时间tWR需要160ns。

3 硬件接口

根据汽车防撞雷达系统的要求,在发送三角波调频信号的同时需采集雷达的回波信号。由于系统资源的限制,我们把A/D和D/A同时配置在TMS320C30的扩展总线上。TMS320C30是TI公司的通用DSP芯片,有很强的浮点/定点数据运算能力和很高的处理速度,特别适合于实时数据采集及运算处理(如FFT,FIR,IIR滤波等)。图3是该接口的硬件连接图。图中,XA[8~10]为扩展总线的地址线中的3条,经过译码器(74LS138)译码后,其输出Y1、Y2分别接到MX7545和MAX153的片选信号(CS)端,分别作为他们的片选信号。RD/WR为TMS320C30扩展总线的读写控制信号,IOSTRB为扩展总线的选通脉冲,XD[0~11]为扩展总线的数据总线。A/D和D/A的读写信号由DSP的扩展总线的读写信号和选通信号来决定,它们的关系可由下式表示:

/WR=RD/WR+IOSTRB

/RD=RD/WR+IOSTRB

当A/D工作时,Y2寻址选中MAX153。DSP的写信号有效时,A/D转换启动;DSP的读信号有效时,A/D输出数据。当D/A工作时,Y1寻址使MX7545有效。DSP的写信号有效时,D/A转换启动。MAX153工作于最快的转换方式,口地址是;MAX7545工作于通用的单极性电流工作模式,口地址是804100。从图中可以看出,其硬件电路是较为简单的。

4 时序的配合和程序的编制

下面将介绍D/A的通用电流工作模式下和A/D在最快工作模式下与TMS320C30 DSP接口的时序配合问题。

4.1 时序配合问题

从系统硬件电路的接法和工作时序上,可以分析"启动转换"和"读取数据"的时序关系。一个假写操作便可使A/D的/WR有效,即可启动转换。就DSP的扩展总线的信号线IOSTRB选通的端口而言,读写都需两个时钟周期。当DSP采用33.3MHz的时钟时,每个时钟周期H1为60ns(即主时钟的二分频)。从图1可见,启动转换时间tWR的最小需要250ns,故需要插入总线等待周期。若插入4个等待周期,此时tWR为60×5=300ns,除去高速译码器的传输延迟17ns,实际WR的脉冲宽度远大于MAX153所规定的tWR的最小脉宽250ns,因而启动A/D转换是可靠的。

由图1可知,MAX153要求的转换时间tRD须大于250ns,故这里需要加入300ns的延迟时间,此时读取A/D转换的数据也是可靠的。接着读取并转换A/D数据,然后向D/A送数据。从图2可以看出,tCS至少需要180ns,tWR至少需要160ns,故设置4个总线等待周期也是完全可满足要求的。

4.2 汇编程序编写

由于此电路用于汽车防撞雷达信号的采集和处理系统中,故此电路应完成的功能是:在发送雷达所需的三角波的同时采集雷达的回波信号,即二者须同时完成。具体程序如下:

根据程序,可以得到系统的时序,如图4所示。

根据以上硬件和软件的设计,由时序图可以得到:

所以,总的转换时间是:

Ts=300+300+300+420+300+60=1680ns

故其转化频率为:

Fs=1/Ts=1/1.68μs=595.2kHz

程序设计中需注意的问题有:

(1)在启动A/D转换前,应先假读一次,使A/D复位,以避免不可靠的操作。

(2)TMS320C30的

- 基于DSP芯片的MELP声码器的算法实现 (03-26)

- TMS320F206外围电路典型设计 (04-17)

- 采用DSP芯片的MELP声码器的算法设计方案(05-06)

- 基于DSP芯片TMS320F240的电压无功控制器的设计(07-30)

- DSP芯片选择方法(07-19)

- 在小尺寸DSP上实现2D条形码解码(09-12)