Xilinx FPGA的Fast Startup

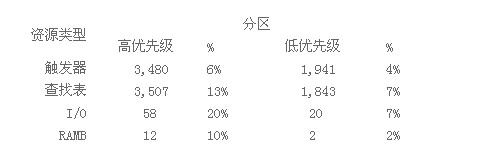

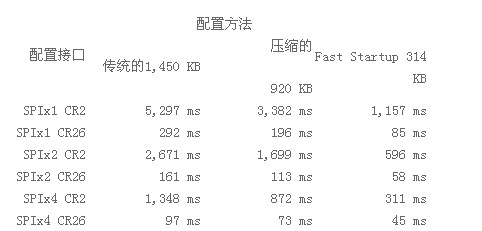

认由网络发包器发送的消息,这条消息立刻重复发送,直至FPGA已经完成其配置并用有效的波特率配置了CAN内核。一旦Spartan-6设计的CAN内核确认了这条消息,网络发包器的CAN内核将触发一个中断,由这个中断停止硬件计时器。该计时器现在保存着SP605设计的引导时间。测量结果包括SP605设计内一个额外的硬件计时器,此结果表明,当执行该软件来配置内置BRAM内存的CAN内核时,软件启动时间可以忽略不计。 表3表示每个分区的FPGA资源消耗。百分比信息是用来表示使用的XC6S45LXT器件的有效资源的总数量。 表3 – Spartan-6设计中占用的FPGA资源 表4 – 测得的Spartan-6配置时间 表4表示配置时间的测量结果。对于这些结果,我们实现并比较了完整设计的一个标准比特流和一个压缩比特流以及使用部分初始比特流的Fast Startup方法。该表列出了针对不同SPI总线带宽和不同配置速率(CR)设置的配置时间。不出所料,配置时间与比特流大小成正比。由于使用快速配置,时钟没有影响清仓过程(housecleaning process),高CR设置的比率(按百分比)发生了变化。 在硬件中验证 我们开发的高级配置方法可以称为优先化的FPGA启动,因为它分两步配置器件。这种方法不仅对于解决现代FPGA中配置时间不断增加的挑战是必不可少,而且也能在很多现代应用中得到使用,如PCI Express或基于CAN的汽车系统。 除了提出高优先级初始配置方法,我们还在硬件中对这种方法进行了验证。我们使用并测试了针对Fast Startup的工具流程和方法,以在Spartan-6评估板(SP605)上实现基于CAN的汽车ECU,以及在Virtex-6原型板上实现视频设计。通过使用这种新颖的方法,我们减小了初始比特流大小,从而使配置时间改进了84%(与标准完整配置方案相比)。 Xilinx将在针对7系列FPGA的软件中支持针对 PCI Express应用的Fast Startup概念,并通过优化的实现方法简化其使用。在7系列中,新的两步比特流方法是实现起来最简单最低成本的方法。设计FPGA时,用户可以通过一个简单的软件开关实现两级比特流。该比特流的第一级仅包含配置时序关键模块需要的配置帧。配置时,会产生一个FPGA STARTUP序列,关键模块变成活动模块,这样就可轻易满足100毫秒时序要求。当时序关键模块运行时(例如PCI Express枚举/配置系统过程正在进行),剩下的FPGA配置得以加载。两级比特流方法能够使用便宜的闪存器件存储比特流。 参考资料 [1]PCI Express底层规范(PCI Express Base Specification),版本1.1,PCI-SIG,2005年3月 [2]M. Huebner, J. Meyer, O. Sander, L.Braun, J. Becker, J. Noguera和R.Stewart, “基于部分及动态重配置的快速顺序FPGA启动”( PCI Express Base Specification),IEEE计算机学会VLSI年度研讨会(ISVLSI),2010年7月 [3]层次设计方法指南,UG748, v12.1, Xilinx,2010年5月 [4]B. Sellers, J. Heiner, M. Wirthlin和J. Kalb, “通过帧摘除和部分重配置压缩比特流”( Bitstream compression through frame removal and partial reconfigura- tion),现场可编程逻辑(和应用国际大会FPL),2009年9月 [5]J. Meyer, J. Noguera, M. Huebner, L. Braun, O. Sander, R. Mateos Gil, R. Stewart, J. Becker, “利用动态部分重配置快速启动Spartan-6 FPGA”( Fast Startup for Spartan-6 FPGAs using dynamic partial reconfiguration),欧洲设计、自动化与测试研讨会(DATE ‘11),2011年 [6]“通过部分重配置快速配置PCI Express技术”( Fast Configuration of PCI Express Technology through Partial Reconfiguration),XAPP883, v1.0, Xilinx, 2010年11月,http://www.xilinx.com/ support/documentation/application_notes/xapp883_Fast_Config_PCIe.pdf.

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)