Xilinx FPGA的Fast Startup

在众多当代应用中,嵌入式系统必须满足极其苛刻的时序要求。其中之一就是启动时间——即上电后电子系统进入可操作状态所需要的时间。PCI Express产品或汽车应用中基于CAN的电子控制单元(ECU)就是具有严格时序要求的电子系统的应用实例。

标准PCI Express(PCIe)系统上电后仅100毫秒,系统的根组件就开始扫描总线以便弄清拓扑结构,并在这一过程中进行初始化配置。 如果PCIe设备没有准备好响应配置请求,根组件就找不到此PCIe设备,并认为它不存在。该设备将无法加入PCIe总线系统。[1]

汽车应用中的情形与此大体相仿。在基于CAN的网络中,ECU进入睡眠模式,这时它们将停止运行并切断电源连接。只有很少部分电路仍然保持戒备状态,以便探测唤醒信号。一旦出现唤醒事件,ECU就会重新连接电源并开始引导。虽然在唤醒事件后的头一个100 毫秒内允许错过一些消息,但在此之后所有ECU都必须在网络(如CAN网络)上做好充分的运行准备。

Xilinx Automotive、Xilinx研究实验室以及德国卡尔斯鲁厄技术研究所之间合作展开了深入的研发工作,正在设法通过一种FPGA两步配置方法解决这一问题。

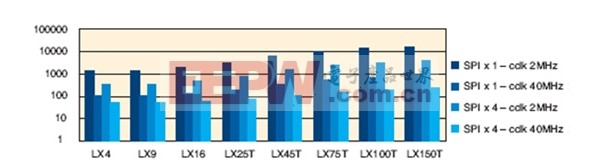

半导体行业的科技趋势已经能使FPGA厂家大大增加其器件中的资源。但比特流规模也在成比例地增长,配置器件需要的时间也是如此。因此,即使对于中等规模的FPGA,使用低成本配置方案也不可能满足严格的启动时序要求。图1表示不同的Xilinx® Spartan®-6 FPGA器件在使用低成本SPI/Quad-SPI配置接口时的配置时间。即使使用快速配置方案(即在40 MHz配置时钟下运行的Quad-SPI),也只有小型FPGA器件才能达到100 毫秒的启动时序要求。对于Xilinx Virtex®-6器件来说,这个结果看来更具挑战性,因为这些器件提供了更丰富的FPGA资源。

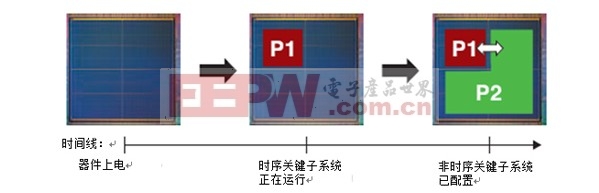

为了克服这个难题,Fast Startup分两步配置FPGA器件,而非单步(整片)的全器件配置。按照这种新颖的思路,我们的策略是在上电时使用最高优先级比特流仅载入时序关键模块,然后再载入非时序关键模块。这种方法最大程度地减少了初始配置数据,从而最大程度地减少了在面向时序关键设计的FPGA器件启动时间。

FAST STARTUP对比部分重配置

Fast Startup允许FPGA设计尽快启动设计的关键模块,关键模块的启动速度比标准全配置方法要快得多[2]。虽然,从本质上来讲Fast Startup利用了部分重配置,但它与这种方法的传统概念所有不同。部分重配置的初衷是将完整设计作为可在运行时修改的初始配置使用。相反,Fast Startup已经使用了一个初始的部分比特流,以在上电时仅仅配置FPGA器件的一个特定(很小的一部分)区域。第一次配置仅包含完整FPGA设计中必须配置和快速运行的那些部分。而剩下的部分则在以后、在运行时,利用部分重配置进行配置。图2说明了这一顺序概念。

工具流程概述

Fast Startup的工具流程依靠设计保存流程,来创建针对时序关键子系统及非时序关键子系统的部分比特流。

设计保存流程将FPGA设计分割为逻辑模块(称为“分区”)。分区构成了层次边界,将内部模块与设计中的其他组件相互隔离。分区一旦实现(即完成布局和布线),就能被其他实现运行导入,以按照每个实例中完全相同的方式实现该分区的模块[3]。

因此,使用Fast Startup方法的第一步是将完整的FPGA设计分成两部分:即含有时序关键子系统的高优先级分区和针对其余组件的低优先级分区。

图1-计算出的Spartan-6配置时间的对数表示(按最坏情况计算)

图2 – Fast Startup概念:顺序配置

高优先级分区的实现

为了得到尽可能小的高优先级分区的部分比特流,设计中有一些一般性问题需要考虑。首先,该分区必须只能包含此类组件:或者是时序关键组件,或者是系统需要这些组件来执行低优先级部分(如ICAP)的部分重配置。得到小规模初始部分比特流的关键是使用尽可能小的区域实现高优先级分区。也就是说,您必须将这个分区局限在FPGA中的一个适当区域中。

为了在FPGA中找到理想的物理位置,这个区域应该提供该设计需要的适当数量的资源。访问该区域以外的资源也是可行的,但我们不鼓励这么做——尽管对于I/O引脚来说,

这样做一般是无法避免的。在寻找适当区域时,还要牢记的是这个FPGA区域有可能会妨碍FPGA设计中非时序关键部分的资源。

当您已经对FPGA进行分区,且已经找到了这些分区的适当区域之后,下一步就是使用一个空的(黑盒子)低优先级分区实现高优先级分区。得到的比特流含有很多针对未使用资源的配置郑您可以删除这些帧,以便得到针对初步配置高优先级分区

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)