基于51单片机的超声波发生器设计方案

本设计的超声波发生器是利用单片机生成初始信号,然后经过一系列处理电路的作用后生成用来杀灭水蚤的超声波,成本低、效果好,可以在农业上加以采用。在此对3个模块进行设计:

(1)信号发生模块。12 MHz的8051单片机硬件连接及其程序设计。

(2)信号处理模块。驱动电路设计(CD4069非门集成芯片);倍频电路设计(S9014或ECGl08三极管、104普通电容、11 257.9 nH自制电感、1 kΩ电阻);整波电路设计(CD4069非门集成芯片);和频电路设计(CD4081与门集成芯片);选频电路设计(S9014或ECGl08三极管、104普通电容、112.58 nH自制电感、1 kΩ电阻)。

(3)信号检测模块、数字示波器的连接。

在上述研究基础上,设计一台超声波发生器样机,其技术指标如下:输入电压:220 VAC(50 Hz);开关频率:1.5~1.8 MHz;最大的输出功率:500 W;功率范围:50~500 W。

1 信号发生模块的设计

选取一个8051单片机芯片,将晶振电路、复位电路、电源电路连接到单片机相应的引脚上组成单片机的最小系统。利用单片机的中断资源和I/O口资源进行相应连接并进行程序编辑:用P3.2口控制初始信号的发射与否,用P0.O口、P0.1口发射初始信号,如图1所示。

2 信号处理模块的设计

2.1 驱动电路的设计

如果将两列波(0.03 MHz)直接从单片机的输出口PO.O和P0.1输出接入后面的5倍频电路,可能会由于电流小而不能驱动倍频电路。从这点来考虑就需要在单片机与倍频电路之间接入一个驱动电路,如图2所示。在单片机的一个输出口接一个非门,而后接入由4个非门并联的电路,由于非门是有源器件,这样就使得输入倍频电路的信号能量大大提高,起到驱动电路的功能(若用方波发生器来代替单片机就可省略驱动电路)。

2.2 倍频电路的设计

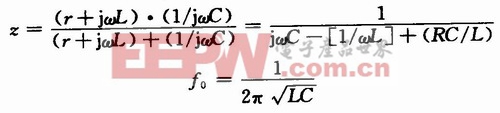

根据电容电感元件的基本特性,以及电路的相关知识可以由已知条件得出:

如图3所示,当在LC并联电路中发生并联谐振时,由电路的特性可知:

并联谐振具有下列特征:

(1)谐振时电路的阻抗摸为|Zo|=1/(RC/L)=L/RC。其值最大,即比非谐振情况下的阻抗摸要大。因此在电源电压U一定的情况下,电路中的电流I将在谐振时达到最小值,即I=IO=U/(L/RC)=U/|Zo|。

(2)由于电源电压与电路中电流同相(∮=0),因此电路对电源呈现电阻性。谐振时电路的阻抗摸|Zo|相当于一个电阻。

(3)谐振时各并联支路的电流为:IL=U/2πfoL;Ic=U/(1/2πfoC),可见IL=Ic>Io,品质因数Q=IL/Io。

(4)当电路发生谐振时,电路阻抗摸最大,电流通过时在电路两端产生的电压也是最大。当电源为其他频率时电路不发生谐振,阻抗摸较小,电路两端的电压也较小。这样就起到了选频的作用。电路的品质因数Q值越大,选择性越强。

通常把晶体管的输出特性曲线分为3个工作区:

(1)放大区。输出特性曲线的近于水平部分是放大区。在放大区,Ic=βIb。放大区也称为线性区,因为Ic和Ib成正比的关系。当晶体管工作于放大区时,发射结处于正向偏置,集电结处于反向偏置,即对NPN型管来说,应使Ube>O,Ubc

(2)截止区。Ib=0的曲线以下的区域称为截止区。Ib=0时,Ic=Iceo。对NPN型硅管而言,当Ube

(3)饱和区。当Uce

LC选频电路接在集电极电路中,通过的交流电流为Ic,其两端交流电压为Uce(即为输出电压),它是并联交流电路。当发生并联谐振时,谐振频率可求得,当将振荡电路与电源接通时,在扰动信号中只有频率为f0的分量才发生并联谐振。在并联谐振时,LC并联电路的阻抗最大,并且是电阻性的(相当于集电极负载电阻Rc)。因此,对f0这个频率来说,电压放大倍数最高,当满足自激振荡的条件时,就产生自激振荡。对于其他频率的分量,不能产生并联谐振,这就达到了选频的目的。在输出端得到的只是频率为f0的信号。当改变LC电路的参数L或C时,输出信号的振荡频率也就改变,于是就可以进行倍频,本实验用的是五倍频,如图4所示。

在实验中已知频率和电容参数计算电感参数,由已知条件可得:Ll=L2=11257.9 nH;L3=112.58 nH。

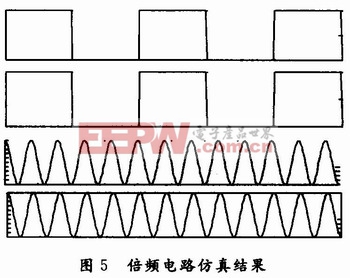

由单片机输出的信号频率即在A1点或A2点(0.03 MHz)经由5倍频放大后输出的信号频率应为输入信号频率的5倍即为A3点或A4点(O.15 MHz),仿真结果如图5所示。

2.3 整波电路的设计

在本实验中运用的是CD4069集成非门电路,非门主要是将输入信号波整合成方波以便于后面与门对波的进一步处理。只要工作电压达到非门的开启电压经过这样的处理就可将输入波整合成方波,如图6所示。

由5倍频放大器输出的信号频率即在A3点或A4点(0.15 MHz)经由两个非门后(即在A5点或A6点)输出的信号应为方波,仿真结果如图7所示。

2.4 和频电路的设计

在本实验中运用的是CD4081集成与门电

- 一种嵌入式时钟管理器的设计与实现(08-01)

- 基于ADC0809和51单片机的多路数据采集系统设计方案(10-29)

- 基于C8051F340驱动与采集的CCD光电遥测垂线仪(02-01)

- ARM仿真器与嵌入式系统设计讲解(02-12)

- 基于单片机C8051F060的智能功率柜的设计应用(01-12)

- 基于单片机的存储设备转储器(05-03)