DM9000A与基带信号处理平台的结合应用

置RCR寄存器,使能数据接收功能。

通过以上步骤,可以通过LED指示灯观测到DM9000A是否已成功初始化。

数据发送模块

DM9000A中的发送缓冲区可以同时存储两帧数据,可以按照先后顺序命名为帧I和帧II。DM9000A上电初始化后,发送缓存区的起始地址是00H,当前数据帧编号为帧I。两帧数据的状态控制字分别记录在DM9000A的状态寄存器03H和04H中。发送过程如下:

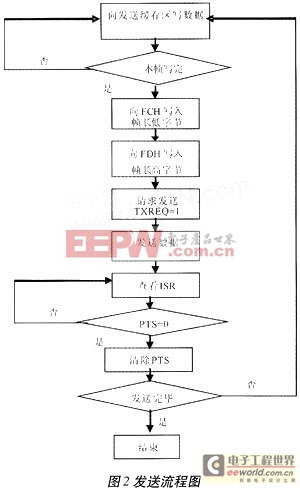

首先,FPGA利用写操作寄存器MWCMD(REG_F8)向DM9000A的发送缓存区中写入发送数据帧,即需要先写入6字节的目的MAC地址,再写入6字节的源MAC地址,最后再写入发送数据。

随后,FPGA利用写操作寄存器MWCMD(REG_F8)将数据帧长度写入寄存器FCH和FDH,数据长度为16位,将高8位写入寄存器FCH,低8位写入寄存器FDH。

最后,FPGA将发送控制寄存器TCR(REG_02)的bit[1]置为高电平,向DM9000A发出发送数据指令。DM9000A会自动做一些处理才将数据发往以太网,这包括:插入报头和帧起始分隔符;插入来自上层协议的数据,如果数据量小于64字节,则自动补齐64字节;根据目标地址、源地址、长度/类型和数据产牛CRC校验序列,并插入校验序列位。这些处理都无需FPGA干预。处理完毕后,DM9000A即开始发送帧I,在帧I发送的同时,帧II的数据即可写入发送缓存区。在帧I发送完后,将帧II的数据长度写入寄存器FCH和FDH,最后将发送控制寄存器NSR(REG_01)的bit[1]置为高电平,即可开始帧II的发送。依此类推,下面发送的帧将会继续编号为帧I、帧II、帧I、帧II……按照同样的方式发送。

如果FPGA将中断屏蔽寄存器 IMR(REG_FF)的bit[1]置为高电平,那么发送完毕后,DM9000A将会产生一个指示发送完成的中断信号。在发送过程中,FPGA可以查询寄存器标志位寄存器NSR(REG_01)中的TX1END bit[2]或者TX2END bit[3],得到数据帧的发送状态。

发送流程如图2所示,寄存器ISR中的PTS标志位是发送中断标志位,当一帧数据发送完毕,PTS=0,FPCA检测到该标志后,应清除标志位以便发送新的数据帧。这里需要注意的是,向FC、FD所写的帧长度应该包含目的MAC地址段、源MAC地址段和有效数据的总长度。

接收模块

DM9000A中的接收缓存区是一个环形结构,初始化后的起始地址为0C00H,每帧数据都有4字节长的首部,然后是有效数据和CRC校验序列。首部4字节依次是01H、状态、长度低字节和长度高字节。

首部4字节含义如下:

第一个字节用来检测接收缓存区中是否有数据,如果这个字节是01H,表明接收到了数据;如果为00H,则说明没有数据。但是,如果第一个字节既不是01H,也不是00H,DM9000A就必须作一次软复位来从这种异常状态中恢复。

第二个字节存储着以太网帧状态,由此可判断所接收帧是否正确。

第三和第四字节存储着以太网帧长度。后续的字节就是有效数据。

接收过程如下:

查看中断状态寄存器,如果接收到新数据,寄存器ISR的PRS位将被置为0;

如果检测到PRS=0,清除PRS,FPGA开始读接收缓存区数据。如果第一字节是01H,则说明有数据,00H说明无数据,否则要进行复位;

根据获取的长度信息,判断是否读完一帧,如果读完,接着读下一帧,直到遇到首字节是00H的帧,说明接收数据已读完。FPGA可以重新查看中断状态寄存器,等待新的有效数据帧。

结语

本文对以太网控制器DM9000A进行了原理和功能介绍,并结合自行开发的SDR基带信号处理平台,基于FPGA设计实现了100M以太刚接口,其设计思路新颖,硬件连接简单。整体系统具有功耗低,体积小,运行稳定可靠等优点。

- 基于DM9000A的以太网接口设计与实现(03-19)

- 基于DM9000A的DSP以太网接口设计与实现(03-12)

- Davicom公司DM9000A和DM9010 ISA NIC 以太网驱动分析(11-02)

- 基于DM9000A的网络接口设计(07-17)

- 以太网接口芯片DM9000A在嵌入式系统中的应用(11-25)

- Windows CE 进程、线程和内存管理(11-09)