Zynq-7000 EPP 开启创新新纪元

赛灵思Zynq-7000 可扩展式处理平台将双 ARM Cortex-A9 MPCore 处理器系统与可编程逻辑和硬 IP 外设紧密集成在一起,提供了顶级的灵活性、可配置性和性能。

赛灵思刚刚推出了可扩展式处理平台(EPP)系列的首款产品,这款革命性架构将双 ARM Cortex™-A9 MPCore 处理器与低功耗可编程逻辑和硬 IP 外设完美集成在同一个器件之上。在今年 3 月,赛灵思正式推出 Zynq-7000 EPP 系列的前四款器件。

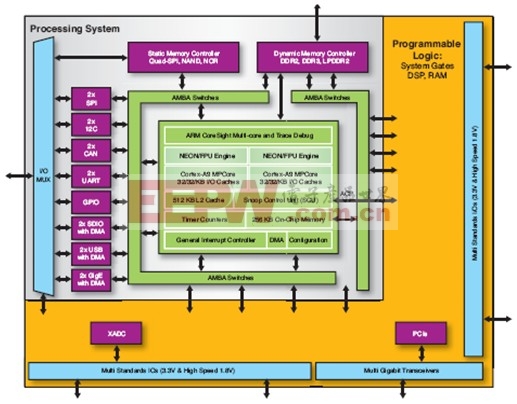

采用 28 nm制造工艺, Zynq-7000嵌入式处理平台系列的每款产品均采用有NEON及双精度浮点引擎的双核 ARM Cortex-A9 MPCore 处理系统,该系统通过硬连线完成了包括L1,L2 缓存、存储器控制器以及常用外设在内的全面集成。(图 1)。尽管 FPGA 厂商此前已推出过采用硬核和软核处理器的器件,但 Zynq-7000 EPP 的独特之处在于它由ARM处理器系统而非可编程逻辑元件来进行控制。也就是说,处理系统能够在开机时引导(在 FPGA 逻辑之前)并运行各个独立于可编程逻辑之外的操作系统。这样设计人员就可对处理系统进行编程,根据需要来配置可编程逻辑。

利用这种方法,软件编程模式将与全功能标准 ARM 处理器片上系统(SoC)毫无二致。过去设计师需要对 FPGA 逻辑进行编程以运行板载处理器。那就意味着如果想要使用器件,那必须得是 FPGA 设计师。但现在使用 Zynq-7000 EPP,则完全不必担心这一问题。

图 1 —— 不同于以往在 FPGA 架构中嵌入 MPU ,赛灵思全新 Zynq-7000 EPP 系列使用 ARM 处理器而非可编程逻辑来进行控制。

图中文字:

新产品系列消除了延迟和从头设计芯片的风险,这意味着系统设计团队可以利用其先进的高级软硬件编程多功能性简便快速创建创新型片上系统,而这是其他任何半导体器件都无法实现的。这样,Zynq -7000 EPP 能够为广大的创新者带来无法比拟的益处,无论是专业的硬件、软件、系统设计师或仅是单纯的“制造商”,他们都可以探讨处理能力与编程逻辑的结合可能性,进而创建出从未想象过的创新应用。

赛灵思处理平台副总裁 Larry Getman 表示:“从最根本的层次来说,Zynq-7000 EPP 应该算是一类全新的半导体产品。它既不是单纯的处理器,也不是单纯的 FPGA。我们的产品是两者的完美结合,正因如此我们才能够帮助您消除现有解决方案的局限性,尤其针对双芯片解决方案和 ASIC。

Getman 称当前大多数电子系统都是将一个 FPGA 和一个独立处理器或一个 ASIC 与相同 PCB 上的一个板载处理器相配对。赛灵思的最新产品可支持使用这类双芯片解决方案的公司利用一个Zynq-7000 芯片来构建下一代系统,节省了物料成本和 PCB 空间,并且降低了总体功率预算。由于处理器和 FPGA 在相同的架构上,因此性能也得到了大幅提升。

Getman 表示 Zynq-7000 EPP 将会加快从 ASIC向 FPGA 的市场迁移。采用最新制造工艺实施 ASIC 过于昂贵并且对大多数应用来说风险太大。因此,越来越多的公司青睐于 FPGA。许多尝试坚守旧 ASIC 方法的公司采用旧的制造工艺来实施他们的设计,分析师称之为“价值认知型片上系统 ASIC”。然而 ASIC 依旧需要较长的设计周期并且存在重新设计(respin)的风险,这样一来费用将会非常昂贵并且可能还会延迟产品的上市时间。Getman 说:“与旧技术相比,借助采用 28 nm技术的 Zynq-7000 EPP,器件的可编程逻辑部分并不存在尺寸或性能损耗的问题,您还可在处理子系统中获得硬化 28 nm片上系统的附加优势。凭借不到 15 美元的起始售价,我们使设计那些产量并非很大的 ASIC 在成本和风险上都不再划算。您可以即刻让您的软硬件团队开工,而那些死守ASIC 的设计团队就很难做到这一点。”

Getman 表示自从赛灵思去年推出这款架构以来,市场反响很好。一部分测试客户(alpha customer)已开始对将使用 Zynq-7000 器件的系统进行原型设计。该技术非常令人兴奋。”

智能架构决策

在赛灵思处理解决方案副总裁 Vidya Rajagopalan 的领导下,Zynq-7000 EPP 设计团队专门针对这类新器件而推出了一款设计精良的架构。除了选择应用广泛且倍受欢迎的 ARM 处理器系统以外,设计团队的一个重要架构决策是在处理系统和可编程逻辑之间广泛使用高带宽 AMBA® 高级扩展接口(AXI™)互联。这样一来便能够以较低的功耗支持 ARM 双核 Cortex-A9 MPCore 处理子系统和可编程逻辑之间的多千兆位数据传输,进而消除了控制、数据、I/O 和内存所面临的性能瓶颈。

实际上,赛灵思一直与 ARM 保持紧密合作,力求让 ARM 架构更

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)