EZ-USB电磁眼接口设计

控制信号时FIFO进行初始化,然后电脑眼的象素同步信号选通FIFO的读数据端口,将电脑眼采集的图像数据写入FIFO;当FIFO中的数据量达到1KB时(即半满时),FIFO自动对半满标志端口置位,EZ-USB2131Q芯片内的控制指令在USB的帧中断时检测到半满标志位后,发出快速读数据控制信号,从FIFO中取出1023个字节的图像数据存入芯片内部的缓冲中。因电脑眼一场图像的分辨率是384×287象素,一场图像数据为110208(1023×107+747)字节,在取完1023×107字节数据后,芯片在USB的下一帧中断时检测不到FIFO半满置位标志。为了保证电脑眼不中断地采集数据而只能舍弃剩余的747字节的数据,并且新的场同步信号的到来又会对FIFO进行初始化,开始存入新一场图像数据。这一接口电路虽然简单,能实现图像显示,但通过USB口所显示的图像不完整。因此,设计了基于外接RAM的单片方案。

2.2 基于外接RAM的单片方案

介于上述接口方案存在的缺陷,即要保证电脑眼不间断采集数据又要保证EZ-USB 2131Q芯片能获取一场图像的全部数据,可以采取如图3所示的另一种单片方案。上面提到过,电脑眼一场的图像数据是110208字节,要存入一场图像数据就需要一个128KB的RAM。为了保证电脑眼不间断地连续传输,在此单片方案中利用一个多路转换器对两个128KB的RAM进行切换,分别存入电脑眼连续采集的两场图像数据。外接RAM的电路中,包含有3大功能块:两个128KB的RAM组成存储功能块、两个地址发生器及一个多路转换器,如图3所示。存储功能块用于存储电脑眼的一场完整图像数据,地址发生器用于存储器的地址选择,多路转换器用于切换对存储块的工作路径。

多路转换器是利用电脑眼场同步信号来进行切换的,其切换频率与电脑眼的场同步信号的频率相当。在多路转换器中,当电脑眼的场同步信号到来时,一路选通RAMA并同时对RAMA写选通,另一路选通RAMB并同时对RAMB读选通。A地址发生器由电脑眼的象素同步信号触发,由此产生的地址信号被接入RAMA的地址端,并将电脑眼采集的一场图像数据写入RAMA中,A地址发生器对RAMB是不选通状态。在EZ-USB芯片端,芯片快速读控制信号触发B地址发生器,产生的地址信号接入RAMB地址端。此时B地址发生器对RAMA是不选通状态,这样USB芯片就能从RAMB中读取完整的一场图像数据。在芯片读取下一场图像数据时,上述过程正好相反,电脑眼向RAMB中写入数据,EZ-USB芯片从RAMA中取出数据。

2.3 基于RAM单片方案的软件流程

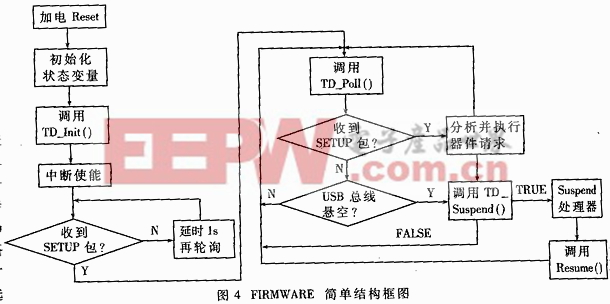

如上所述,EZ-USB 2131Q芯片采用了一种基于RAM的方案,实现数据格式转换的程序并未固化在芯片中,是一种软硬结合的固件(FIRMWARE)。当器件插入USB口时,主机对器件进行轮询,获取了器件的ID号后,系统程序将FIRMWARE下载到芯片内部,执行数据格式的逻辑转换。FIRMWARE结构如图4所示。其中:TD_Init():用于初始化FIRMWARE的全局状态变量;TD_Poll():反复调用,用于执行用户的外设功能;TD_Suspend():此函数可以使器件进入低功耗状态;TD_Resume():此函数用于响应外部恢复事件,使器件恢复正常工作状态。

FIRMWARE工作时,获取图像数据后转换成USB数据格式,提交给计算机处理。

利用FIFO的方法,电路简单,可以得到稳定的图像。但代价是要丢掉一些有效数据,在不损失有效数据的条件下又必须控制电脑眼,会使得图像的传输速率降。是一种可用但不最佳的方法。

电脑眼基于外接RAM的单片方案,虽然在电路上比接FIFO稍显复杂,但此方案解决了数据传输的完整性,而且能保持电脑眼连续采集数据,保证了电脑眼的最大传输速率。

图5是通过基于RAM的单片方案获取电脑眼采集的图像数据并经USB口送入计算机,经过客户软件处理后得到的电脑眼的图像。

综上所述,基于外接RAM的单片方案是一种稳定可以的解决方案,保证了数据的完整性和连续性。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)