基于DSPBuilder的FIR滤波器的方案设计

时间:12-31

来源:互联网

点击:

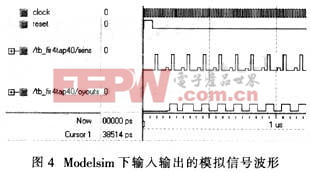

仿真波形,可以看到这与Simulink里的仿真结果基本一致,即可在QuartusⅡ环境下进行硬件设计。

4.5 在FPGA器件中实现FIR滤波器

在QuartusⅡ环境中打开DSPBuilder建立的QuartusⅡ项目文件firl.qpf。在QuartusⅡ中进行再一次仿真,由此可以看到符合要求时序波形,然后指定器件引脚并进行编译,最后下载到FPGA器件中,就可以对硬件进行测试,加上CLCOK信号和使能信号,用信号发生器产生所要求的两个不同频率的正弦信号,就可以在示波器上看到滤波以后的结果,需要设计不同的滤波器电路时,仅修改FIR滤波模型文件就可以实现,这样不仅避免了繁琐的VHDL语言编程,而且便于进行调整。

5 结束语

在利用FPGA进行数字滤波器的开发时,采用DSPBuilder作为设计工具能加快进度。当然,在实际应用中,受精度、速度和器件选择方面的影响,可以对其转化的VHDL进行进一步的优化。

方案设计 滤波器 FIR DSPBuilder 基于 相关文章:

- 基于XML技术的考试阅卷系统方案设计(10-30)

- 基于单片机的智能家居安防系统方案设计(10-14)

- 基于CAN总线的电梯外呼系统方案设计(10-06)

- 基于Virtex-5 FPGA的音视频监视系统方案设计(10-06)

- 基于单片机的智能家居安防系统的方案设计(09-26)

- 基于OuartusⅡ和GW48EDA开发工具的电子抢答器方案设计(09-16)