基于Virtex-5 FPGA的音视频监视系统方案设计

引言

本文探讨在Virtex-5 FPGA中实现设计的一些难题,然后用一个项目作为示范来详解充分利用其功能集的技法。设计过程包括几个步骤,从针对应用选择适合的Virtex-5开始。为便于本文叙述,我们假定IP模块已经过汇编,并且已经就绪备用或已经用CORE Generator生成。

针对应用选择适合的器件

多数音视频采集器件都支持单信道,以Y/Cr/Cb数据格式生成源同步数字信号。DSP虽然有能力采集数字音视频信号,也能够执行数字信号处理任务,但通常却仅支持少数几条信道。本设计选择了FPGA,事实证明这对于多信道输入任务和信号处理任务都是良好的替代方案。

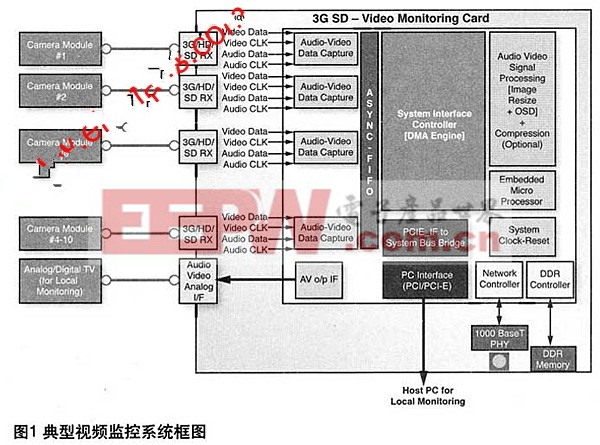

图1所示为典型的安全视频监视系统,其中有一个3G/SD/HD/SDI视频接口。在此设计中,摄像头将3G—SDI格式的信息传送到电路板,后者继而收集数据,并且以145.5MHz的最高时钟频率将其转换成10位(Y/Cr/Cb格式)的源同步视频数据(10/20位的接口)。电路板以 96kHz的最高时钟频率处理源同步音频数据。

这里,存储器的容量是512Mb,宽度是32位,所以FPGA必须支持高达2Gb的扩展能力。

对于这个设计来说,FPGA必须支持多达十条数字音视频源同步输入信道(20位源同步Y/Cr/Cb数据格式),并且必须可按照SD/HD数据格式配置。其他要求还包括音视频信号处理和可选压缩算法、带有高级DMA引擎的中央处理单元和一个用来连接VGA显示器或标准型电视机的音视频输出端口等。

要满足这些技术条件,在实现设计时必须考虑几个因素。其中的主要因素是时钟要求分析、初始布局规划、核生成和IP集成、时序约束定义以及布局布线后的时序分析和时序校正。但首先要决定FPGA的选择。

FPGA的选择

我们根据几个因素进行选择。器件需要满足预计的I/O要求,并且必须具有相应数量的逻辑单元、适宜的Block RAM尺寸以及一定数量的时钟缓冲器和时钟管理器件,如锁相环(PLL)、数字时钟管理(DcM)模块和乘累加模块。基于这些需求,我们选择了 Virtex-5 XCVSX95T-FF1136。

时钟要求分析

选择FPGA之后,我们开始设计过程,即分析时钟控制要求,然后将信号映射到I/O组或I/O引脚。

对于时钟要求分析,重要的是考虑以下几个因素:FPGA是否具有足够的时钟功能I/O线和全局时钟I/O线?是否有足够的PLL、DCM和全局时钟缓冲器?全局时钟I/O缓冲器是否支持所要求的最高频率?

本设计的时钟控制要求包括:一个以150MHz-200MHz频率运行的全局系统时钟,具有若干PLL供所有内部逻辑用来进行处理;一个以 250MHz频率运行的全局时钟,具有PLL/DCM的PCI Express链接;一个以250MHz频率运行的全局时钟缓冲器(带有PLL和DCM)用于以太网MAC;以及一个200MHz的时钟(由 PLL/DCM生成),用于I/O模块中的逐位去歪斜等。

我们总共需要4~6个全局时钟缓冲器和16个局部时钟缓冲器。FPGA XCVSX95T-FF1136提供每组20个全局时钟输入引脚和4个时钟功能I/O。也可将I/O组的时钟功能引脚直接连接到区域缓冲器或I/O缓冲器,并且将其用于特定区域或相邻区域。另外,各GTP/MGT还有一个参考时钟输入引脚。

初始布局规划

初始布局计划是设计的关键阶段,因为此时所作的决定将确定最终设计是否能满足时序。其中组选择和引脚分配是布局规划的重要步骤。如何进行这两个步骤取决于FPGA周围其他组件的布局。

Virtex—5 FPGA共有18个I/O组,可以将各种输入/输出对映射到这些I/O组。有几个I/O组支持20对输入/输出或10个全局时钟。其他I/O组则大多支持 40对输入/输出,每对输入/输出上有4个输入时钟功能引脚和8个输出时钟功能引脚。

同时,上下两牛个FPGA包括三个时钟控制模块(CMT),即一个PLL和两个DCM。对于需要上下两半个器件中的PLL的所有全局时钟信号,我们必须确保予以妥善映射,以使设计具有从全局时钟输入缓冲器到PLL的直接连接。然后我们使用剩下的14个I/O组,这些组支持40条I/O线,是单端/差分模式。每个组由4个单端时钟功能引脚和8个差分时钟功能引脚组成。接下来可以将时钟功能引脚映射或连接到区域时钟缓冲器或I/O时钟缓冲器。

一般情况下,可以使用这些时钟功能引脚和区域缓冲器来映射源同步时钟输入。区域缓冲器具有较低歪斜度,可以访问三个区域(一个区域缓冲器所在的区域,以及其上和其下各一个区域)。但对于源同步数据的组选择,我们倾向于只使用一个I/O组。如果需要其他IIO,则最好将I/O组用于已事先映射到相邻组的数据信号。

设计的初始布局规划按照几个步骤进行。首先将系统时钟放在上半部,然后将自动采集(可选)时钟放在下半部。我们锁定了每半部分的CMT,以满足 I/O组的3/4要求。这样映射能确保每半部分都留有两个P

系统 方案设计 监视 音视频 Virtex-5 FPGA 基于 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)