基于ISP技术的图像处理系统设计

随着图像处理技术应用的普及,其应用范围越来越广。在医学、军事、公安等领域,特别是近些年在工业自动化、工业检测方面得到广泛应用。目前的图像处理系统大多采用计算机加上视频采集卡和摄像头来构成其硬件系统,这种硬件结构对于处理自满不复杂的简易图像处理系统显然是不合适的。

目前,EPLD芯片内部的资源越来越多,速度越来越快,开发的软件功能也更加完善,使其应用逐步扩大。人们普遍认为,今后的许多电子系统,将以CPU+RAM+EPLD的结构为特征。图像系统将向小型化发展。如何设计一套简单的、低成本的图像处理系统是将图像处理技术应用到更广的领域的迫切要求。

本文介绍的系统正是针对这样的需求而开发出来的。

1 总体设计方案

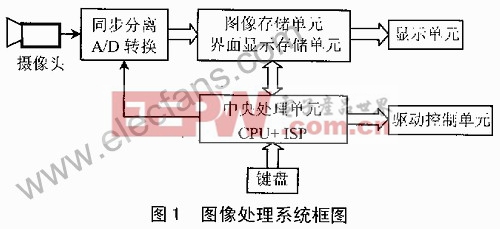

整个系统由摄像头、图像输入单元、图像存储单元、图像处理单元、图像显示单元及驱动控制单元几部分组成。图像处理系统框图如图1所示。

该图像处理系统采用Atmel的89C55为中央处理单元,系统时钟为20MHz。图像采集部分由ISPLSI1032E提供存储图像RAM的地址信号和采集图像点阵的时钟信号。根据需要每帧图像可分为256×256或512×512点阵,在特殊情况下也可采用256×128或512×256半屏方式。在图像输出单元,可将图像与显示菜单迭加输出,构成可视菜单。

另外,为适应工业检测和工业自动化方面的应用,在系统中还设计了驱动控制电路,可以输出开关量和模拟量。基本上能够适应各种控制场合。

2 硬件电路设计

2.1 ISP器件开发

ISP器件除具有一般PLD器件所具有的易用性、高性能和FPGA的灵活性、高密度外,最重要的一条是它的在系统可编程技术,即ISP可以在空白的状态下焊接到电路板上。任何已经安装好ISP器件的电路板,只要通过PC机和下载电缆,就能升级新的编程代码,并且一切工作可在不断电的前提下进行。

ISP(In SYSTEM PROGRAMMING)技术是LATTICE半导体公司首先提供出来的一种能在产品设计、制造过程中的每个环节,甚至在产品卖给最终用户以后,随时对其器件、电路板或整个电子系统的逻辑和功能进行组态或重组的最新技术。

在系统开发过程中,图像采集的核心部分是视频信号经A/D转换的结果如何存储到存储器中,即如何根据视频信号产生存储器的地址信号。经过对所需逻辑门数量的估算,我们采用ISPLSI1032为地址发生器和其它一些逻辑电路。

2.2 图像采集时序的产生

这里,以256×128点阵为例,说明图像采集时序的产生。

以A0~A7表示每行中点阵的地址,A8~A14表示行地址。其行有效信号和A0~A7地址的时序如图2所示,其场有效信号和A8~A14地址的时序如图3所示。这样共用256×128=32

768个存储单元存储1幅图像。

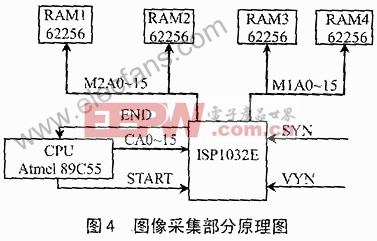

如果需要采集图像,由由CPU给ISP发出START信号,令ISP断开CPU提供给图像RAM的地址线,改由ISP产生图像RAM的地址A0~A14。SIP产生完1幅图像的地址后,输出1个END信号,通知CPU采图完毕,并让出RAM的地址线和数据线给CPU,供其进行图像处理。

系统中共有4片32K×8bit的RAM(62256),其中:

RAM1为图像帧存;

RAM2为图形标志位,用于图像的标注;

RAM3为菜单界面的显存;

RAM4为系统内存,用来存储处理的中间数据和处理结果。

图4为图像采集部分原理图。

在实际使用中,CPU对RAM1、RAM4与RAM2、RAM3的操作是分时进行的。在扫描期,CPU对RAM1和RAM4进行操作,进行图像的计算和结果处理;而在回扫期,则进行菜单和标注的刷新。ISP对RAM2和RAM3的操作是在扫描期,进行菜单和标注与图像的合成输出。

ISPEXPERT的LATTICE公司于20世纪90年代末推出的一套完整的ISP集成开发环境。它有500个宏元件可供调用,支持VHDL、Verilog-HDL、ABELHDL和原理图编译器一体的开发软件;可用于ISP器件的逻辑设计和优化、逻辑映射、自动布局布线、生成熔丝图文件和编程下载。此外,它还可以对设计的数字系统进行功能仿真、时序仿真和静态时序分析。

从使用者的角度看,ISPEXPERT比Workview office和Synario软件功能更强大,操作更方便。

本系统采用ISP1032E芯片省略了复杂的、大量的逻辑电路,利用VHDL语言编程,通过ISPEXPERT集成开发环境开发,既节省了大量的硬件调试时间,又减少了线路间的相互干扰。更重要的是节省了重复制板的时间,大大缩短了产品开发周期。

结束语

基于ISP和单片机构成的图像处理系统,具有结构简单、集成度高、体积小、价格低廉等特点,尤其适用于具有图像处理功能的嵌入式系统的开发。本系统已在实际中使用,取得了良好的效果。

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 嵌入式可重构的多DSP图像并行处理系统(01-26)

- 基于μC/OS-II+CPLD的电动车电池管理系统设计(09-14)

- ARM和DSP设计的地震加速度信号处理系统(01-04)