嵌入式可重构的多DSP图像并行处理系统

时间:01-26

来源:

点击:

随着多媒体图像处理应用的迅速发展,体积小、重量轻、结构灵活、处理能力强的嵌入式数字图像处理系统在工业、医学等方面都有越来越广泛的需求。实时性高、计算复杂、数据量大是图像处理系统面临的重大挑战。并行计算是提高处理速度最有效的技术之一,图像并行处理技术为提高图像处理效率提供了广阔的空间。图像并行处理包括并行算法和多处理器并行硬件系统,图像处理并行算法的执行效率依赖于多处理器系统的硬件结构。通常,一种并行结构只适合于一类并行算法的映射。

20世纪90年代至今,图像并行处理技术一直是图像处理领域研究的热点之一。参考文献分别对并行处理结构及其实现方法进行了探讨,提出了流水结构、分列并行等很有价值的硬件并行结构框架。目前,图像并行处理结构设计面临的主要问题可以概括为两个方面:

②面向图像处理算法的硬件结构针对性设计方法导致图像处理平台的可重用性差,调整、扩展和升级困难。

本文构建的可重构并行计算系统可以通过配置可重构处理单元来满足不同应用的计算要求。这样的系统使图像处理结构设计与图像处理的算法设计分离,具有很高的性能并且结构灵活,能大大提高图像处理并行算法的执行效率和加速比。

1 传统图像并行处理技术

1.1 图像并行处理系统概述

目前,用于嵌入式图像处理系统的高速器件主要是DSP和FPGA。处理核心的合理选用是影响并行系统处理能力的一个关键因素。

并行处理的目的是通过采用多个处理单元同时处理输入信息来缩短任务的执行时间。在任务和算法确定的情况下,Amdahl定律可表明:加速比与任务并行度和处理单元个数密切相关。在任务并行度一定的情况下,增加处理单元所获得的加速比有一个极限值,任务的并行度制约着并行处理机的性能。

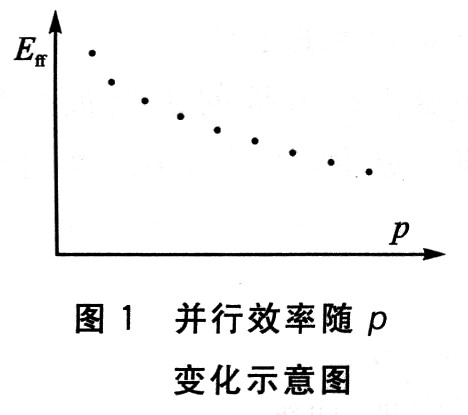

在实际应用中,还必须考虑各个处理单元之间的数据交换和同步时间。由于比串行程序执行增加了数据通信和同步等待等开销,因此当加速比Sp 在增加处理单元和任务细粒度化的同时将带来总通信量的增加,影响了Sp的增加并导致Eff呈下降趋势,如图1所示。

并行计算处理单元之间的网络结构大致可分为2种:一种是共享总线或共享存储器系统,称为"紧耦合式并行系统",如图2所示;另一种是各处理单元有独立的数据存储器而通过通信口相连的分布式并行系统,称为"松耦合式系统",如图3所示。

1.3 并行算法到并行结构的映射

一个任务要在多处理机系统上得到处理,首先必须将其分解成一些子任务,再由多处理系统中的各处理机分别处理这些子任务,协同完成该任务。如图4所示,并行算法在并行硬件系统上的应用是一个映射过程。一类并行算法依赖于适合的并行网络结构才能高效率地运行。

20世纪90年代至今,图像并行处理技术一直是图像处理领域研究的热点之一。参考文献分别对并行处理结构及其实现方法进行了探讨,提出了流水结构、分列并行等很有价值的硬件并行结构框架。目前,图像并行处理结构设计面临的主要问题可以概括为两个方面:

②面向图像处理算法的硬件结构针对性设计方法导致图像处理平台的可重用性差,调整、扩展和升级困难。

本文构建的可重构并行计算系统可以通过配置可重构处理单元来满足不同应用的计算要求。这样的系统使图像处理结构设计与图像处理的算法设计分离,具有很高的性能并且结构灵活,能大大提高图像处理并行算法的执行效率和加速比。

1 传统图像并行处理技术

1.1 图像并行处理系统概述

目前,用于嵌入式图像处理系统的高速器件主要是DSP和FPGA。处理核心的合理选用是影响并行系统处理能力的一个关键因素。

并行处理的目的是通过采用多个处理单元同时处理输入信息来缩短任务的执行时间。在任务和算法确定的情况下,Amdahl定律可表明:加速比与任务并行度和处理单元个数密切相关。在任务并行度一定的情况下,增加处理单元所获得的加速比有一个极限值,任务的并行度制约着并行处理机的性能。

在实际应用中,还必须考虑各个处理单元之间的数据交换和同步时间。由于比串行程序执行增加了数据通信和同步等待等开销,因此当加速比Sp 在增加处理单元和任务细粒度化的同时将带来总通信量的增加,影响了Sp的增加并导致Eff呈下降趋势,如图1所示。

并行计算处理单元之间的网络结构大致可分为2种:一种是共享总线或共享存储器系统,称为"紧耦合式并行系统",如图2所示;另一种是各处理单元有独立的数据存储器而通过通信口相连的分布式并行系统,称为"松耦合式系统",如图3所示。

1.3 并行算法到并行结构的映射

一个任务要在多处理机系统上得到处理,首先必须将其分解成一些子任务,再由多处理系统中的各处理机分别处理这些子任务,协同完成该任务。如图4所示,并行算法在并行硬件系统上的应用是一个映射过程。一类并行算法依赖于适合的并行网络结构才能高效率地运行。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)