基于JTAG仿真器的DSP中断检测处理技术方案设计

以应用在印刷电路板的连通性测试领域,通过将 JTAG器件的边界扫描链连接在一起,并且控制合适的数据信息在该扫描链中传递,从扫描链的输出端进行监控就可以判别有关印刷电路板连通性以及元器件功能等方面的问题。

基于 JTAG技术的仿真器是用来进行芯片硬件仿真,如程序单步执行、设置中断检测点等,通过硬件仿真可以了解芯片里面程序的详细运行情况。 JTAG仿真器主要用来对芯片进行仿真操作,同时也可以通过 JTAG接口对芯片编程(将程序写入芯片)。它的接口方式有LPT(并行)口,PCI或ISA卡,USB口。JTAG仿真器一端通过USB口与PC机连接, 另一端通过 JTAG插头与 DSP目标板连接;建议首先连接 JTAG仿真器到 PC机, 再连接到 DSP目标板。[8] 3、基于 TMS320 C54XDSP芯片的信号发生器

3.1 TMS320 C54x系列 DSP芯片

TMS320 C54x系列 DSP芯片是使用静态 CMOS技术制造的。该芯片采用改进哈佛结构,对程序内存和数据内存使用分离的总线;可以同时取指令和操作数,提高了运行效率和通用性先进的 CPU设计和为应用设计的硬件逻辑提高了芯片的性能;为快速的后续发展设计了模块化的结构;为先进的 IC处理技术提供了高性能和低功耗;高度专门的指令结构提供了快速运算和优化的高阶语言操作;具有单指令循环和块指令循环功能;块内存移动指令提供了更好的程序和数据管理;拥有两个或三个操作数读取能力的指令;从中断快速返回的指令拥有多种片上外设和内存配置方案等特点。

3.2信号发生器

一 )连接硬件,首先给 DSP目标扳加电,指示灯亮。

一 CCS运行环境。

一 )建立新项目,并在项目中添加相关文件。

一 Project 菜单中 open选项,在弹出的对话框中选择信号发生器的编译工程。

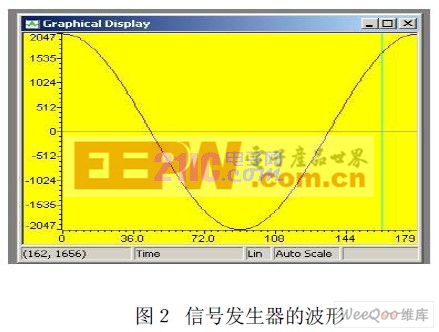

一 Project 菜单中 Rebuild All选项,编译链接该工程,没有错误后,选择 File菜单中 Load Program选项,选择 *.C文件,进行加载程序。选择 View菜单中 graph选项中 Time/Frequency设置图形属性,选择 Start Address 为 dacdata ,设 Acquisition Buffer Size为 180 ,设 Display Data Size为180 ,设 Dsp Data Type为 16-bit signed integer。点击 OK ,观察信号发生器的波形,如图2:

处理 技术 方案设计 检测 中断 JTAG 仿真器 DSP 基于 相关文章:

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- Altera FPGA在Fairlight新媒体处理引擎中替代64片DSP(01-20)

- 基于DSP的短波分集合成接收机(09-01)

- LPC2292的伪中断与伪中断处理(03-25)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)