嵌入式微处理器IP core设计与分析

摘要:本文在对传统微控制器进行系统分析的基础上,提出了一种较好的改进设计方法。回避了传统微控制器基于累加器的ALU结构及算术逻辑指令:并在指令执行时序上尽量减少指令执行所需的时钟周期。通过仿真验证证明该设计方法提高了指令的执行效率和微控制器的运行效率,同时避免了通常采用并行处理设计中多级流水线设计带来的内部复杂的控制逻辑设计。

关键字:微控制器;IP core;流水线

在嵌入式系统的设计中,IP技术为SoC的设计提供了有效途径,是SoC的技术支撑。当然,在国内开发出具有自主知识产权的IP模块还面临着许多问题,如核心算法的优化、不同层次模块的建立、模块的可重用问题以及IP模块的标准化问题等。对于嵌入式处理器IP核,面对的挑战就是如何选择一个满足其应用需求的处理器。现已有数百种嵌入式处理器,每组都具备一组不同的外设、存储器、接口和性能特性,用户很难做出一个合理的选择。本文设计的微处理器的指令集与标准8051单片机完全兼容,这样有利于开发人员的使用。

1 总体设计方案的拟定

1.1 提出改进方案

首先在对典型八位微处理器进行了详尽地剖析的基础上,指出在传统典型微处理器内核中制约微处理器整体性能的主要因素,然后提出以下改进方案:

(1)微处理器的内核结构上,将乘、除法单元各自独立出来来完成算术逻辑指令中的乘、除法运算。这样可以回避传统典型微处理器基于累加器的ALU结构及算术逻辑指令,从而提高逻辑指令的执行效率。

(2)在指令系统上,通过采用类RISC的指令系统和硬布线直接产生控制信号的方式来简化指令译码器的设计。同时为内核添加指令缓冲区、采用指令流水线技术、多管道并行执行指令。

(3)指令时序上,设计中尽量减少指令执行所需的时钟周期,提高微处理器的运行效率。

1.2 总体设计思路

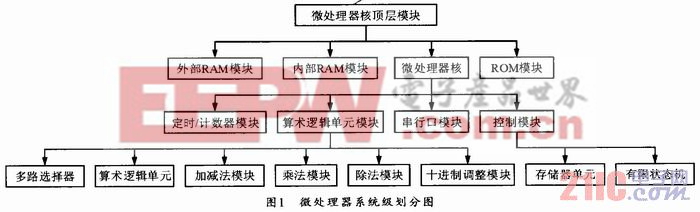

根据IP core通用的设计方法,本文采用了标准的自顶向下的设计方法。就是根据系统级的内容,把系统划分为单元,然后再把每个单元划分为下一层次的单元,这样一直划分下去,直到最底层的单元可以用硬件描述语言进行设计,如图1所示;接着在完成各个模块设计的基础上完成系统级设计;然后进行整个系统的仿真验证;最后选用特定的FPGA芯片进行综合、布局布线以及功能后仿真。

2.1 ALU模块

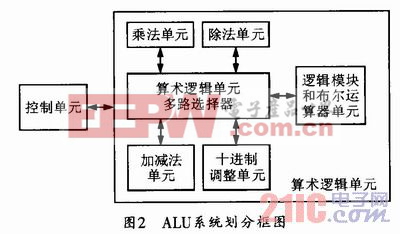

算术逻辑单元(ALU)是微控制器的核心部件,ALU的设计依赖于指令系统,ALU采用什么样的结构、设置那些功能都是建立在对系统指令集分析的基础上来完成。

根据算术运算类指令可知,ALU单元主要要完成的功能有:带/不带进位加/减法、乘法、除法、十进制调整、逻辑运算以及布尔操作的实现。整个操作的完成是通过多路选择器控制来完成。因此,我们可以对整个ALU系统进行如图2划分,然后对各个子模块进行设计。

2.2 控制通路的设计

本文中的控制通路由译码器模块和控制器模块两部分组成。这部分的设计是在对指令系统进行正确分析的基础上来完成。

设计控制通路有两种主要的方法。微程序控制(或微序列控制)方式使用存储器查表方式来输出控制信号,而硬连线控制使用时序逻辑和组合逻辑来产生控制信号。硬件直接实现的控制单元一般用有限状态机实现,通常有较高的运算速度;但是通用性差,每个电路都必须专门设计控制单元。每一种方法都有一些变形形式。由于本文中微处理器的控制相对简单,所以在设计中采用了硬连线控制方法。

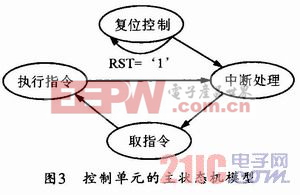

(1)控制器模块的状态机实现

根据本文中多数输出要保持一个完整的时钟周期,此时钟周期内输出不能受时钟信号的影响,所以采用Moore型有限状态机来完成控制器模块的设计。整个控制模块的设计通过主状态机和子状态机两步来完成。注状态机模型如图3所示。

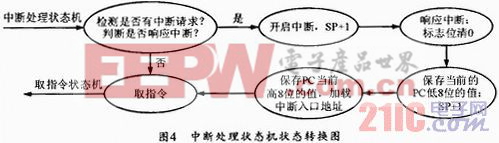

以中断处理子状态机设计为例,对子状态机的设计进行说明,状态转换图如图4所示。

(2)存储器模块的设计

存储器是数字系统的重要组成部分,数据处理单元的处理结果需要存储,许多处理单元的初始化数据也需要存放在存储器中。本文的存储器结构,采用的是将程序存储器和数据存储器分开寻址的哈佛结构。同时又将数据存储器分为内部数据存储器和外部数据存储器两部分来设计。

(3)中断系统设计

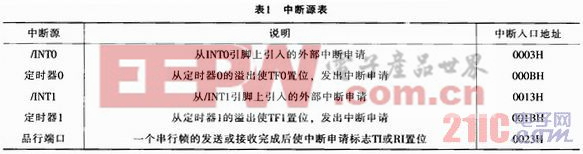

本文中的中断系统在控制通路来完成,共提供了5个中断源,同时通过对中断优先级寄存器IP中的某位的置位或清除,可以把每个中断源分别编程为高优先级或低优先级。如表1所示。

(4)定时器/计数器模块的设计

定时器/计数器是微处理器中重要的外围模块,它主要是完成作为定时器和事件计数器的功能。在作为定时器工作时,每一个机器周期使定时寄存器加1计数。在作为事件计数器工作时,是对外部输入负跳变信号做加法计数,规定在每个机器周期的某一状态采样此信号,在前一个周期采样到“1”,后一个周期采样到“0”时计数加1,而在检测到跳变信号后的那个周期的下一个状态时,新的计数值装入计数寄存器。

3 系统综合、仿真验证与性能分析

在整个微处理器IP核的设计过程中,利用可编程逻辑器件进行电路验证对于保证设计的正确性和投片成功十分重要。在FPGA的设计流程中包括三种基本的验证方法:HDL、RTL级描述仿真,门级仿真和布线后的时序仿真。具体验证流程如图5所示。仿真的目的就是要确认设计的正确性。如果出错的话,则通过分析仿真器的输出波形,找出出错的原因,并对原设计进行修改。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)